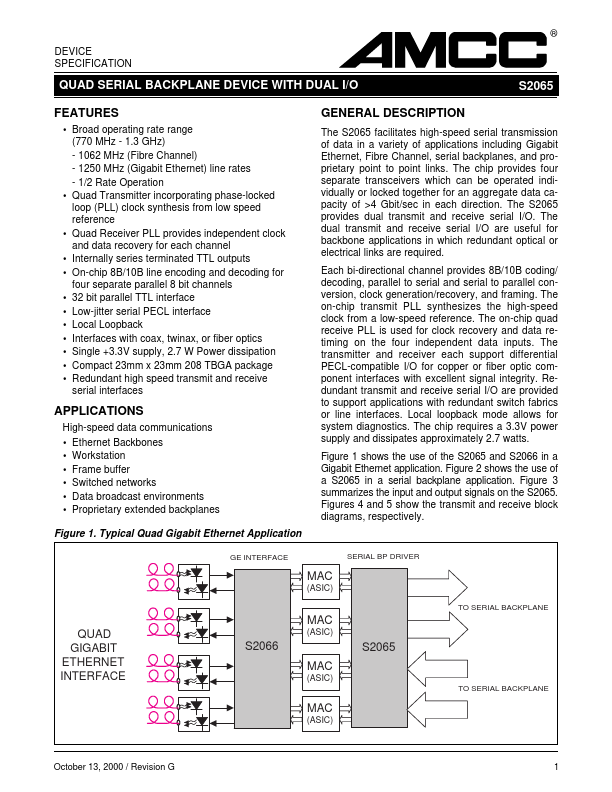

S2065

Overview

- Broad operating rate range (770 MHz - 1.3 GHz) - 1062 MHz (Fibre Channel) - 1250 MHz (Gigabit Ethernet) line rates - 1/2 Rate Operation

- Quad Transmitter incorporating phase-locked loop (PLL) clock synthesis from low speed reference

- Quad Receiver PLL provides independent clock and data recovery for each channel

- Internally series terminated TTL outputs

- On-chip 8B/10B line encoding and decoding for four separate parallel 8 bit channels

- 32 bit parallel TTL interface

- Low-jitter serial PECL interface

- Local Loopback

- Interfaces with coax, twinax, or fiber optics

- Single +3.3V supply, 2.7 W Power dissipation