S2202

Key Features

- 1250 MHz (Gigabit Ethernet) operating rate .. - Half rate operation

- Dual Transmitter with phase-locked loop (PLL) clock synthesis from low speed reference

- Dual Receiver PLL provides clock and data recovery

- Internally series terminated TTL outputs

- Low-jitter serial PECL interface

- Individual local loopback control

- JTAG 1149.1 Boundary scan on low speed I/O signals

- Interfaces with coax, twinax, or fiber optics

- Single +3.3V supply, 1.85 W power dissipation

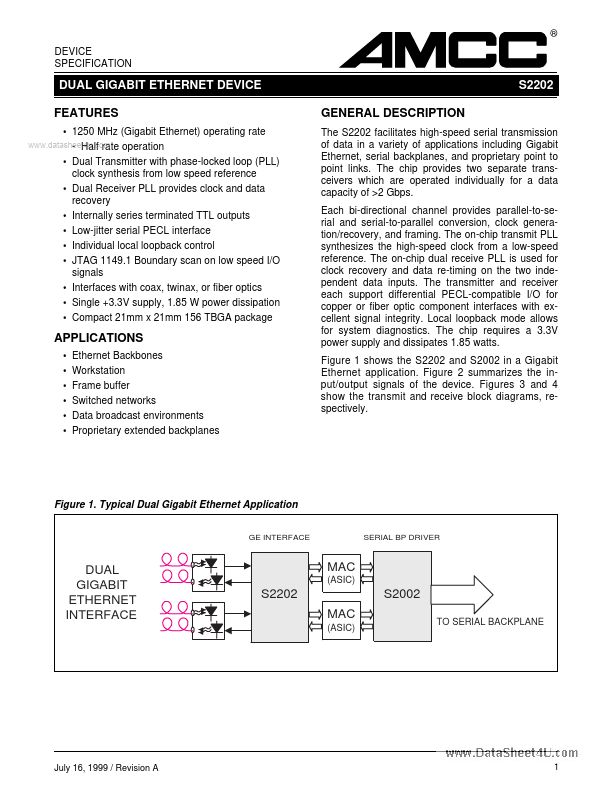

- pact 21mm x 21mm 156 TBGA package The S2202 facilitates high-speed serial transmission of data in a variety of applications including Gigabit Ethernet, serial backplanes, and proprietary point to point links. The chip provides two separate transceivers which are operated individually for a data capacity of >2 Gbps. Each bi-directional channel provides parallel-to-serial and serial-to-parallel conversion, clock generation/recovery, and framing. The on-chip transmit PLL synthesizes the high-speed clock from a low-speed reference. The on-chip dual receive PLL is used for clock recovery and data re-timing on the two independent data inputs. The transmitter and receiver each support differential PECL-patible I/O for copper or fiber optic ponent interfaces with excellent signal integrity. Local loopback mode allows for system diagnostics. The chip requires a 3.3V power supply and dissipates 1.85 watts. Figure 1 shows the S2202 and S2002 in a Gigabit Ethernet application. Figure 2 summarizes the input/output signals of the device. Figures 3 and 4 show the transmit and receive block diagrams, respectively.