Datasheet Summary

Document Title 16M X 16 Bit DDR DRAM

Revision History

Rev. No. History

1.0 Initial issue

16M X 16 Bit DDR DRAM

Issue Date

January 9, 2014

Remark

Final

(January, 2014, Version 1.0)

AMIC Technology, Corp.

16M X 16 Bit DDR DRAM

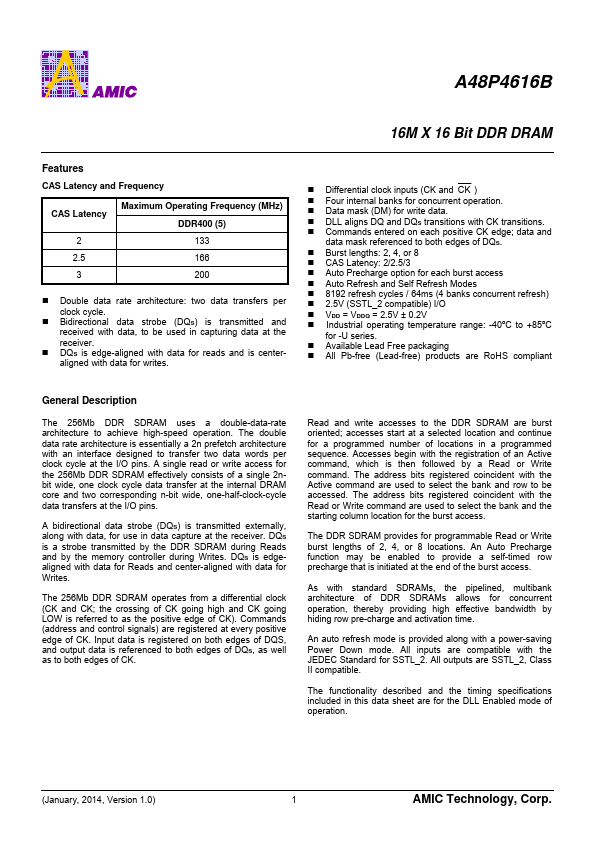

Features

CAS Latency and Frequency

CAS Latency

2 2.5 3

Maximum Operating Frequency (MHz) DDR400 (5) 133 166 200

- Double data rate architecture: two data transfers per clock cycle.

- Bidirectional data strobe (DQS) is transmitted and received with data, to be used in capturing data at the receiver.

- DQS is edge-aligned with data for reads and is centeraligned with data for writes.

- Differential clock inputs (CK and CK )

- Four internal...