Datasheet Summary

..

LP62S1024B-I Series

128K X 8 BIT LOW VOLTAGE CMOS SRAM

Document Title 128K X 8 BIT LOW VOLTAGE CMOS SRAM Revision History

Rev. No.

0.0 0.1 1.0 1.1 1.2

History

Initial issue Add 32L Pb-Free TSSOP package type Final version release Change ICCDR1, ICCDR2 (max.) from 3μA to 1μA Add Pb-Free package type for all parts

Issue Date

May 30, 2002 October 2, 2002 July 18, 2003 June 29, 2004 August 9, 2004

Remark

Preliminary Final

(August, 2004, Version 1.2)

AMIC Technology, Corp.

LP62S1024B-I Series

128K X 8 BIT LOW VOLTAGE CMOS SRAM

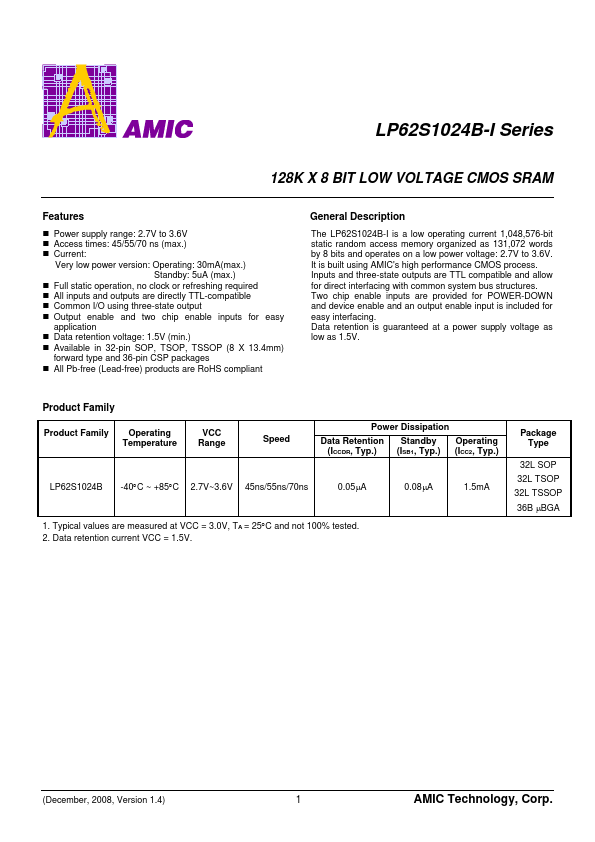

Features

- Power supply range: 2.7V to 3.6V

- Access times: 55/70 ns (max.)

- Current: Very low power version: Operating: 30mA(max.) Standby:...