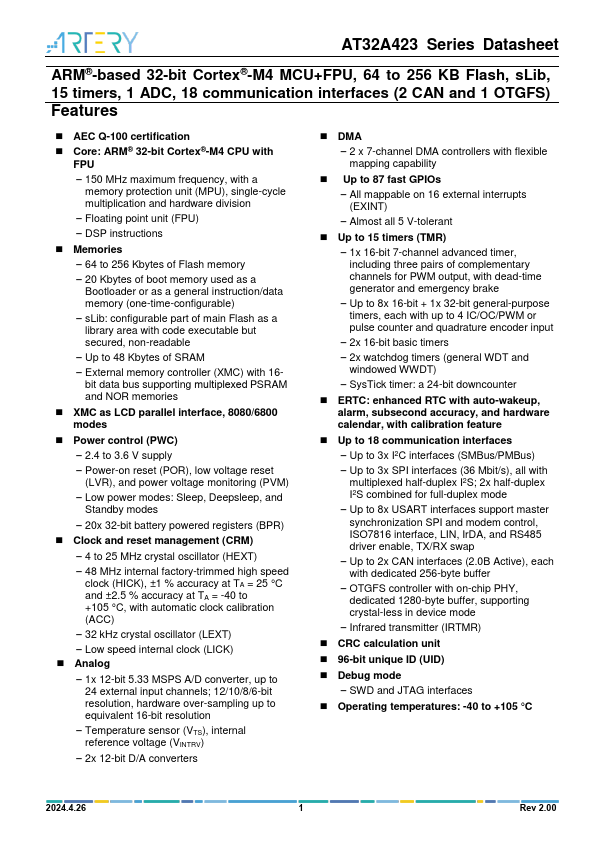

AT32A423

AT32A423 is 32-bit MCU+FPU manufactured by ARTERY.

Features

- AEC Q-100 certification

- Core: ARM® 32-bit Cortex®-M4 CPU with FPU

- 150 MHz maximum frequency, with a memory protection unit (MPU), single-cycle multiplication and hardware division

- Floating point unit (FPU)

- DSP instructions

- Memories

- 64 to 256 Kbytes of Flash memory

- 20 Kbytes of boot memory used as a Bootloader or as a general instruction/data memory (one-time-configurable)

- s Lib: configurable part of main Flash as a library area with code executable but secured, non-readable

- Up to 48 Kbytes of SRAM

- External memory controller (XMC) with 16bit data bus supporting multiplexed PSRAM and NOR memories

- XMC as LCD parallel interface, 8080/6800 modes

- Power control (PWC)

- 2.4 to 3.6 V supply

- Power-on reset (POR), low voltage reset (LVR), and power voltage monitoring (PVM)

- Low power modes: Sleep, Deepsleep, and Standby modes

- 20x 32-bit battery powered registers (BPR)

- Clock and reset management (CRM)

- 4 to 25 MHz crystal oscillator (HEXT)

- 48 MHz internal factory-trimmed high speed clock (HICK), ±1 % accuracy at TA = 25 °C and ±2.5 % accuracy at TA = -40 to +105 °C, with automatic clock calibration (ACC)

- 32 k Hz crystal oscillator (LEXT)

- Low speed internal clock (LICK)

- Analog

- 1x 12-bit 5.33 MSPS A/D converter, up to 24 external input channels; 12/10/8/6-bit resolution, hardware over-sampling up to equivalent 16-bit resolution

- Temperature sensor (VTS), internal reference voltage (VINTRV)

- 2x 12-bit D/A converters

- DMA

- 2 x 7-channel DMA controllers with flexible mapping capability

- Up to 87 fast GPIOs

- All mappable on 16 external interrupts (EXINT)

- Almost all 5 V-tolerant

- Up to 15 timers (TMR)

- 1x 16-bit 7-channel advanced timer, including three pairs of plementary channels for PWM output, with dead-time generator and emergency brake

- Up to 8x 16-bit + 1x 32-bit general-purpose timers, each with up to 4 IC/OC/PWM or pulse counter and quadrature encoder input

- 2x 16-bit basic timers

- 2x watchdog timers (general...