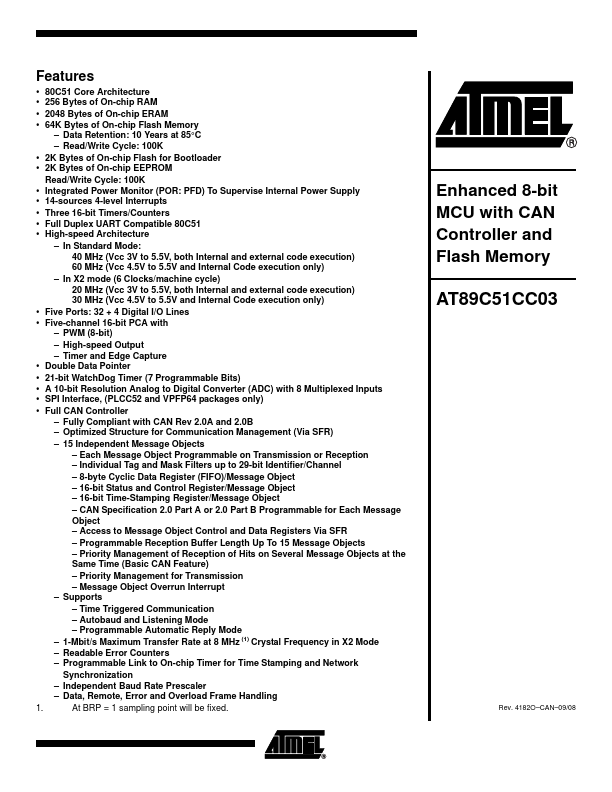

AT89C51CC03

AT89C51CC03 is Enhanced 8-bit MCU manufactured by Atmel.

- Part of the AT89 comparator family.

- Part of the AT89 comparator family.

Features

- 80C51 Core Architecture

- 256 Bytes of On-chip RAM

- 2048 Bytes of On-chip ERAM

- 64K Bytes of On-chip Flash Memory

- Data Retention: 10 Years at 85°C

- Read/Write Cycle: 100K

- 2K Bytes of On-chip Flash for Bootloader

- 2K Bytes of On-chip EEPROM Read/Write Cycle: 100K

- Integrated Power Monitor (POR: PFD) To Supervise Internal Power Supply

- 14-sources 4-level Interrupts

- Three 16-bit Timers/Counters

- Full Duplex UART patible 80C51

- High-speed Architecture

- In Standard Mode:

40 MHz (Vcc 3V to 5.5V, both Internal and external code execution) 60 MHz (Vcc 4.5V to 5.5V and Internal Code execution only)

- In X2 mode (6 Clocks/machine cycle) 20 MHz (Vcc 3V to 5.5V, both Internal and external code execution) 30 MHz (Vcc 4.5V to 5.5V and Internal Code execution only)

- Five Ports: 32 + 4 Digital I/O Lines

- Five-channel 16-bit PCA with

- PWM (8-bit)

- High-speed Output

- Timer and Edge Capture

- Double Data Pointer

- 21-bit Watch Dog Timer (7 Programmable Bits)

- A 10-bit Resolution Analog to Digital Converter (ADC) with 8 Multiplexed Inputs

- SPI Interface, (PLCC52 and VPFP64 packages only)

- Full CAN Controller

- Fully pliant with CAN Rev 2.0A and 2.0B

- Optimized Structure for munication Management (Via SFR)

- 15 Independent Message Objects

- Each Message Object Programmable on Transmission or Reception

- Individual Tag and Mask Filters up to 29-bit Identifier/Channel

- 8-byte Cyclic Data Register (FIFO)/Message Object

- 16-bit Status and Control Register/Message Object

- 16-bit Time-Stamping Register/Message Object

- CAN Specification 2.0 Part A or 2.0 Part B Programmable for Each Message Object

- Access to Message Object Control and Data Registers Via SFR

- Programmable Reception Buffer Length Up To 15 Message Objects

- Priority Management of Reception of Hits on Several Message Objects at the Same Time (Basic CAN...