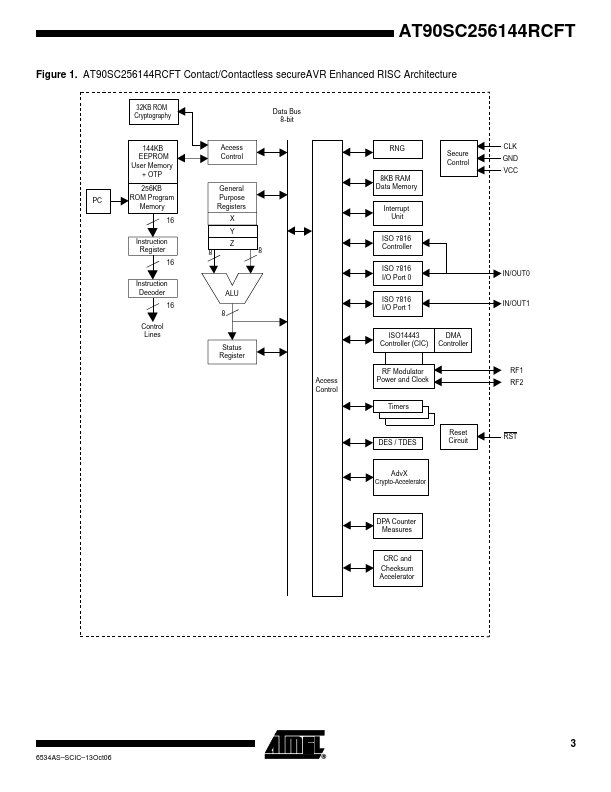

Datasheet Summary

Features

General

- -

- -

- -

- High-performance, Low-power secureAVR Enhanced RISC Architecture

- 137 Powerful Instructions (Most Executed in a Single Clock Cycle) Low Power Idle and Power-down Modes Bond Pad Locations Conforming to ISO 7816-2 ESD Protection to ± 6000V Operating Ranges: 2.7V to 5.5V pliant with ICAO and FIPS201 Specifications, GSM and EMV2000 Specifications Available in Wafers, Contact Modules, Dual Interface Modules, Full Contactless Modules or Inlays and Industry-standard Packages

Contactless Mode

RF Contactless Interface with Full Support for ISO/IEC 14443 Type A and B Protocols Supply Voltage Clamp and Regulation Full-bridge Power Rectification On-chip Tuning...