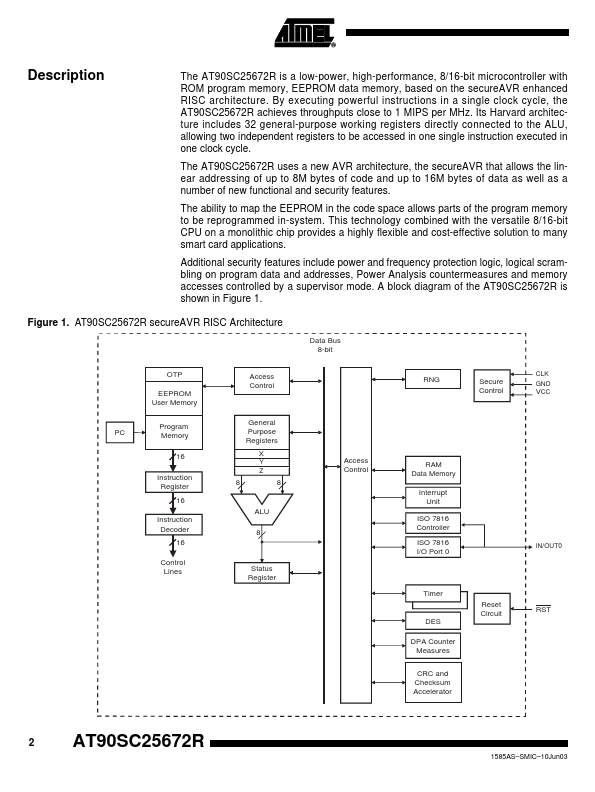

Datasheet Summary

..

Features

General

- -

- -

- -

- High-performance, Low-power secureAVR Enhanced RISC Architecture

- 133 Powerful Instructions (Most Executed in a Single Clock Cycle) Low-power Idle and Power-down Modes Bond Pad Locations Conforming to ISO 7816-2 ESD Protection to ± 6000V Operating Ranges: from 2.7V to 5.5V pliant with GSM, 3GPP and EMV 2000 Specifications; PC Industry patible Available in Wafers, Modules and Industry-standard Packages

Memory

- 256K Bytes of ROM Program Memory

- 72K Bytes of EEPROM, Including 128-byte OTP Area and 384-byte Bit-addressable

Bytes

- 1 to 128-byte Program/Erase

- 1 ms Program, 1 ms Erase

- Typically More than 500,000 Write/Erase...