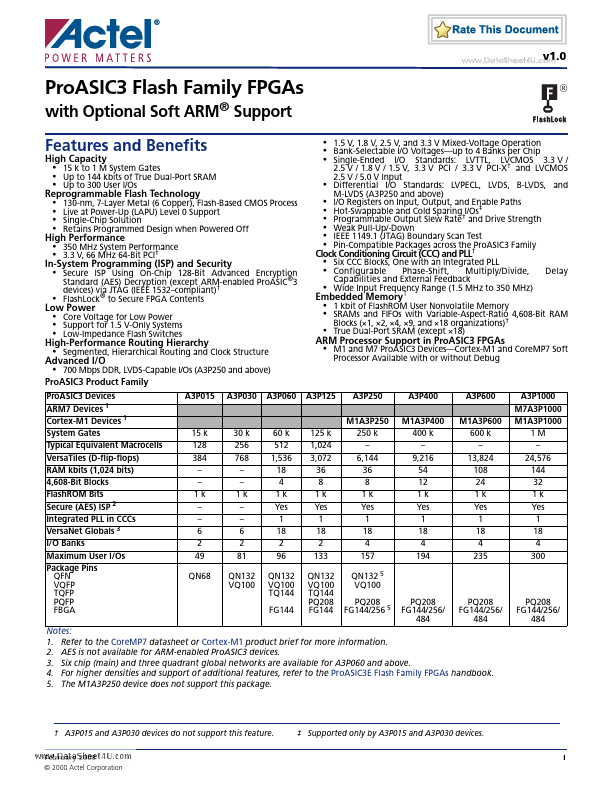

M1A3P250 Key Features

- 15 k to 1 M System Gates

- Up to 144 kbits of True Dual-Port SRAM

- Up to 300 User I/Os

- 130-nm, 7-Layer Metal (6 Copper), Flash-Based CMOS Process Live at Power-Up (LAPU) Level 0 Support Single-Chip Solution

- 350 MHz System Performance

- 3.3 V, 66 MHz 64-Bit PCI†

- 1.5 V, 1.8 V, 2.5 V, and 3.3 V Mixed-Voltage Operation

- Bank-Selectable I/O Voltages-up to 4 Banks per Chip

- Single-Ended I/O Standards: LVTTL, LVCMOS 3.3 V / 2.5 V / 1.8 V / 1.5 V, 3.3 V PCI / 3.3 V PCI-X† and LVCMOS 2.5 V / 5.0

- Differential I/O Standards: LVPECL, LVDS, B-LVDS, and M-LVDS (A3P250 and above)