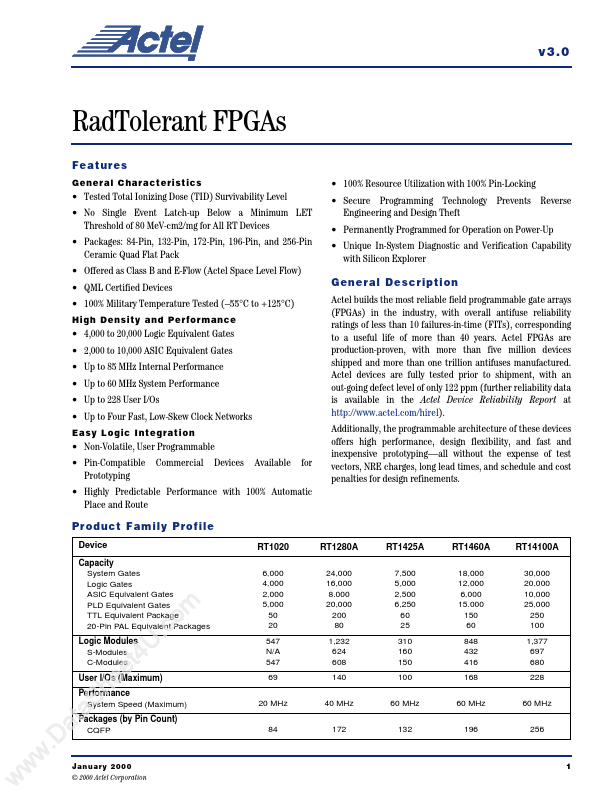

- Part: A1020B

- Description: FPGAs

- Manufacturer: Actel

- Size: 1.12 MB

Datasheets by Manufacturer

| Part Number | Manufacturer | Description |

|---|---|---|

| A102Jxxxx | BC | Leaded ceramic multilayer capacitors |

| A1029 | Hitachi Semiconductor | 2SA1029 |

| V23076-A1022-C133 | TE Connectivity | Power Relay |

| Q62702-A1025 | Siemens Semiconductor Group | Silicon PIN Diode |

| Q62702-A1028 | Siemens Semiconductor Group | Silicon Schottky Diode |

| KYL-A102 | Shenzhen KYL Communication | Low Power ASK Receiver |

| A102VW01-V8 | AU Optronics | TFT LCD |

| V23133-A1022-C133 | Tyco Electronics | PCB relays |

| A1024 | FGX | PNP Transistor |

| MC9080-A102x | ueno | SMD Common mode choke coils |