A6833

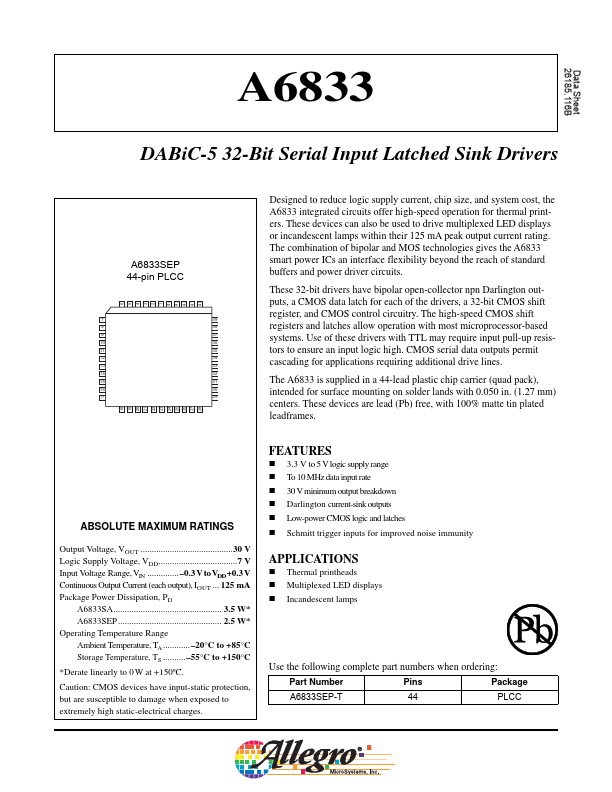

A6833 is DABiC-5 32-Bit Serial Input Latched Sink Drivers manufactured by Allegro MicroSystems.

..

Data Sheet 26185.116B

DABiC-5 32-Bit Serial Input Latched Sink Drivers

Designed to reduce logic supply current, chip size, and system cost, the A6833 integrated circuits offer high-speed operation for thermal printers. These devices can also be used to drive multiplexed LED displays or incandescent lamps within their 125 mA peak output current rating. The bination of bipolar and MOS technologies gives the A6833 smart power ICs an interface flexibility beyond the reach of standard buffers and power driver circuits. These 32-bit drivers have bipolar open-collector npn Darlington outputs, a CMOS data latch for each of the drivers, a 32-bit CMOS shift register,...