Datasheet Summary

Revision History

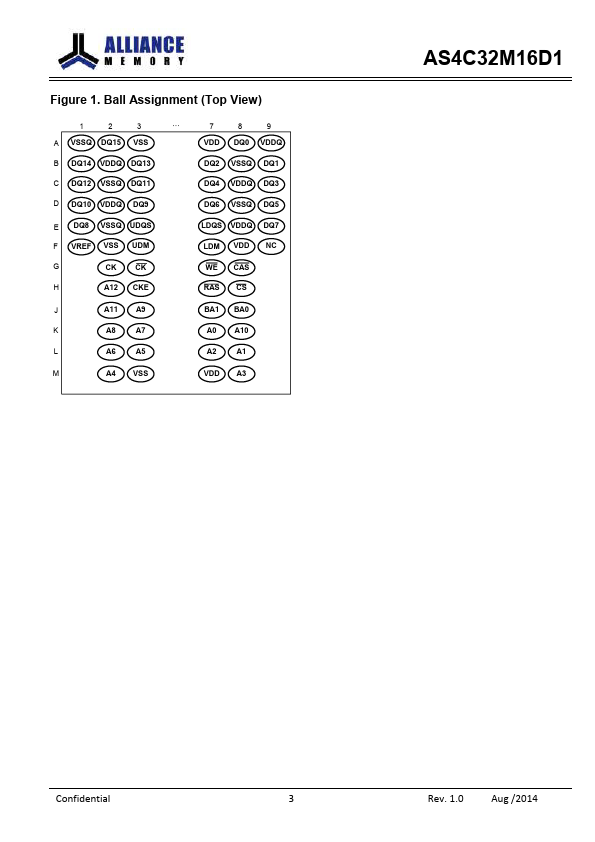

- 60-Ball, 8x13x1.2 mm (max) TFBGA PACKAGE

Revision Details Rev 1.0 Preliminary datasheet

Date August 2014

Confidential

Rev. 1.0

Aug. /2014

32M x 16 bit DDR Synchronous DRAM (SDRAM)

TFBGA option

- Advanced (Rev. 1.0, Aug. /2014)

Features

- Fast clock rate: 200MHz

- Differential Clock CK & CK

- Bi-directional DQS

- DLL enable/disable by EMRS

- Fully synchronous operation

- Internal pipeline architecture

- Four internal banks, 8M x 16-bit for each bank

- Programmable Mode and Extended Mode registers

- CAS Latency: 2, 2.5, 3

- Burst length: 2, 4, 8

- Burst Type: Sequential & Interleaved

- Individual bytes write mask control

-...