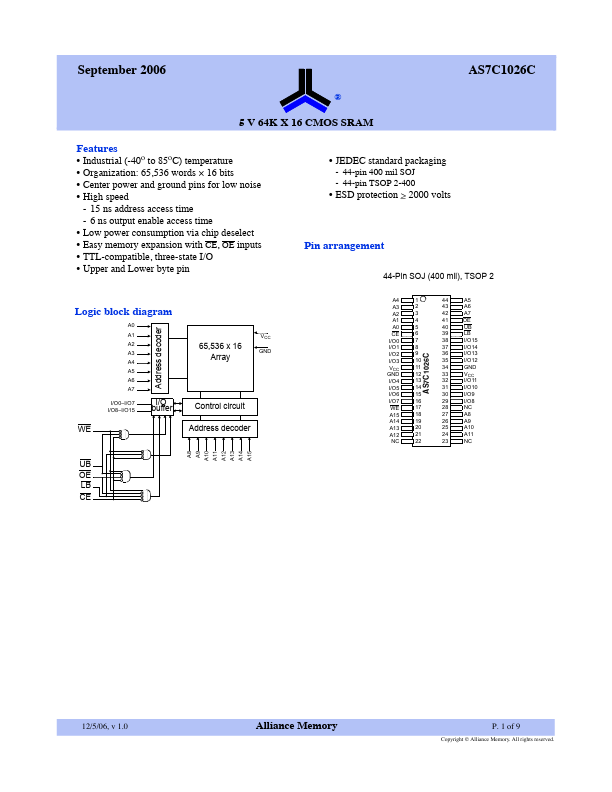

| Part | AS7C1026C |

|---|---|

| Description | 5V 64K x 16 CMOS SRAM |

| Manufacturer | Alliance Semiconductor |

| Size | 287.41 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| AS7C1025B | Alliance Semiconductor Corporation | 5V 128K x 8 CMOS SRAM |

| AS7C1024B | Alliance Semiconductor Corporation | 5V 1Mb FAST Asynchronous SRAM |