AS8C403600

AS8C403600 is 3.3V Synchronous SRAMs manufactured by Alliance Semiconductor.

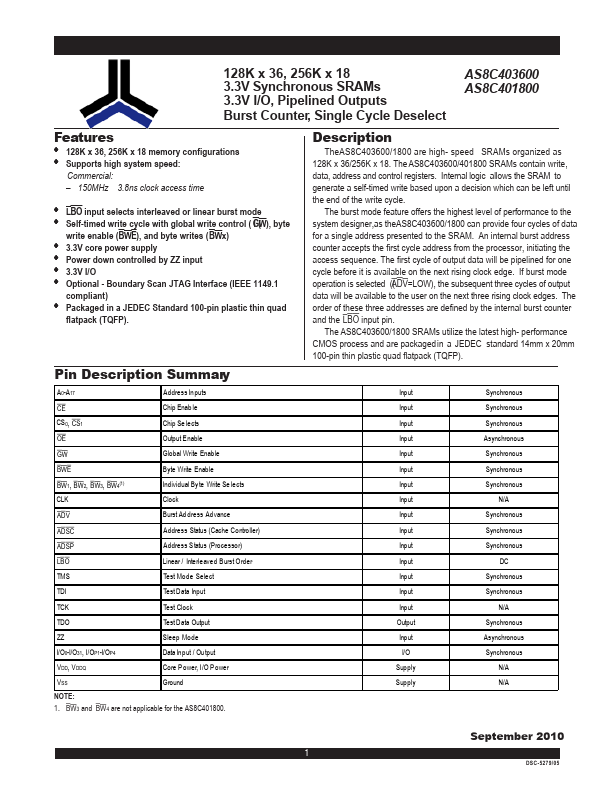

128K x 36, 256K x 18 3.3V Synchronous SRAMs 3.3V I/O, Pipelined Outputs Burst Counter, Single Cycle Deselect

- -

AS8C403600 AS8C401800

Features

128K x 36, 256K x 18 memory configurations Supports high system speed: mercial:

- 150MHz 3.8ns clock access time LBO input selects interleaved or linear burst mode Self-timed write cycle with global write control ( GW l ( ), byte write enable (BWE), and byte writes ( BWx) 3.3V core power supply Power down controlled by ZZ input 3.3V I/O Optional

- Boundary Scan JTAG Interface (IEEE 1149.1 pliant) Packaged in a JEDEC Standard 100-pin plastic thin quad flatpack (TQFP).

Description

- -

- -

- -

- TheAS8C403600/1800 are high- speed SRAMs...