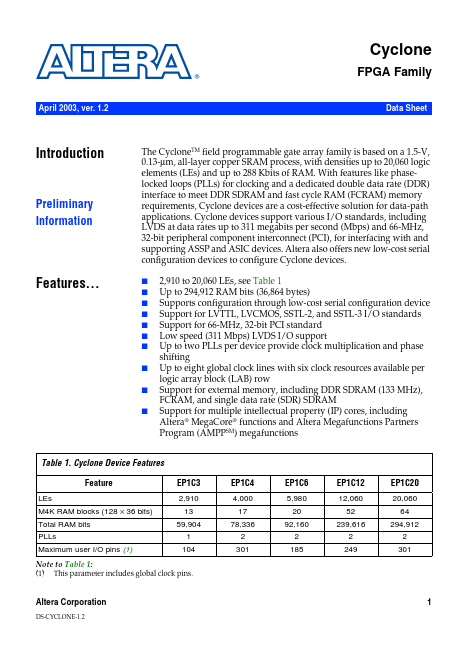

| Part | EP1C3 |

|---|---|

| Description | FPGA |

| Manufacturer | Altera |

| Size | 1.08 MB |

Pricing from 102.768 USD, available from CoreStaff and Verical.

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| CoreStaff | 5 | 1+ : 102.768 USD 2+ : 99.445 USD 3+ : 98.337 USD 4+ : 97.783 USD |

View Offer |

| Verical | 67166 | 2+ : 40.85 USD 25+ : 34.72 USD 100+ : 23.15 USD 500+ : 19.85 USD |

View Offer |

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| EP1S-4N3TT | NEC | LOW SOUND PRESSURE |

| EP1 | NEC | Twin relay for motor and solenoid reversible control |

| EP1-3G3 | NEC | Twin relay for motor and solenoid reversible control |

| EP1-3L1 | NEC | Twin relay for motor and solenoid reversible control |

| EP1-4L3 | NEC | Twin relay for motor and solenoid reversible control |