AD6653

AD6653 is IF Diversity Receiver manufactured by Analog Devices.

FEATURES

SNR = 70.8 d Bc (71.8 d BFS) in a 32.7 MHz BW at 70 MHz @ 150 MSPS

SFDR = 83 d Bc to 70 MHz @ 150 MSPS 1.8 V analog supply operation 1.8 V to 3.3 V CMOS output supply or 1.8 V LVDS output supply Integer 1-to-8 input clock divider Integrated dual-channel ADC

Sample rates up to 150 MSPS IF sampling frequencies to 450 MHz Internal ADC voltage reference Integrated ADC sample-and-hold inputs Flexible analog input range: 1 V p-p to 2 V p-p ADC clock duty cycle stabilizer 95 d B channel isolation/crosstalk Integrated wideband digital downconverter (DDC) 32-bit, plex, numerically controlled oscillator (NCO) Decimating half-band filter and FIR filter Supports real and plex output modes Fast attack/threshold detect bits posite signal monitor Energy-saving power-down modes

APPLICATIONS munications Diversity radio systems Multimode digital receivers (3G)

TD-SCDMA, Wi Max, WCDMA, CDMA2000, GSM, EDGE, LTE I/Q demodulation systems Smart antenna systems General-purpose software radios Broadband data applications

PRODUCT HIGHLIGHTS

1. Integrated dual, 12-bit, 125 MSPS/150 MSPS ADC. 2. Integrated wideband decimation filter and 32-bit plex NCO. 3. Fast overrange detect and signal monitor with serial output. 4. Proprietary differential input maintains excellent SNR performance for input frequencies up to 450 MHz. 5. Flexible output modes, including independent CMOS, interleaved CMOS, IQ mode CMOS, and interleaved LVDS. 6. SYNC input allows synchronization of multiple devices. 7. 3-bit SPI port for register programming and register readback.

AVDD

VIN+A VIN- A

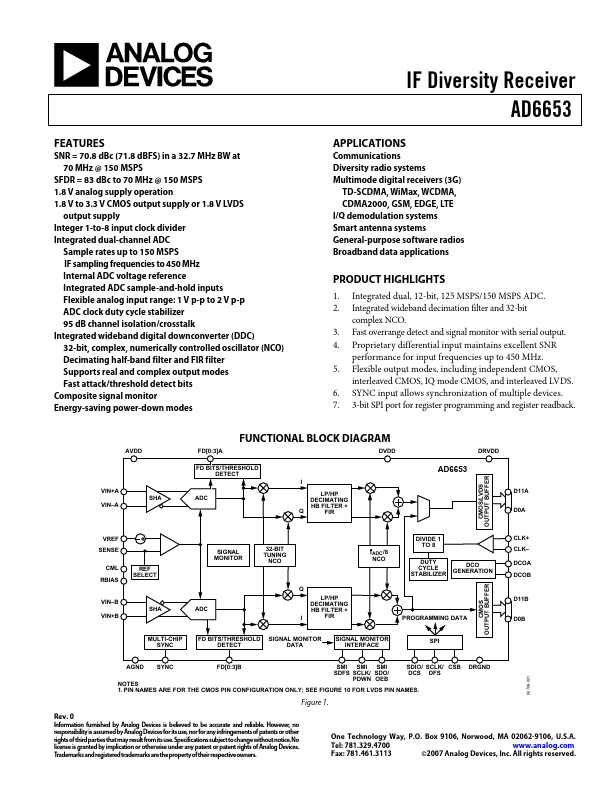

FUNCTIONAL BLOCK DIAGRAM

FD[0:3]A

DVDD

FD BITS/THRESHOLD DETECT

LP/HP

DECIMATING

HB FILTER +

DRVDD

D11A D0A

CMOS/LVDS OUTPUT BUFFER

VREF SENSE

CML RBIAS

REF SELECT

VIN- B VIN+B

SIGNAL MONITOR

32-BIT TUNING

LP/HP

DECIMATING

HB FILTER +

FIR f ADC/8...