AD9528

Overview

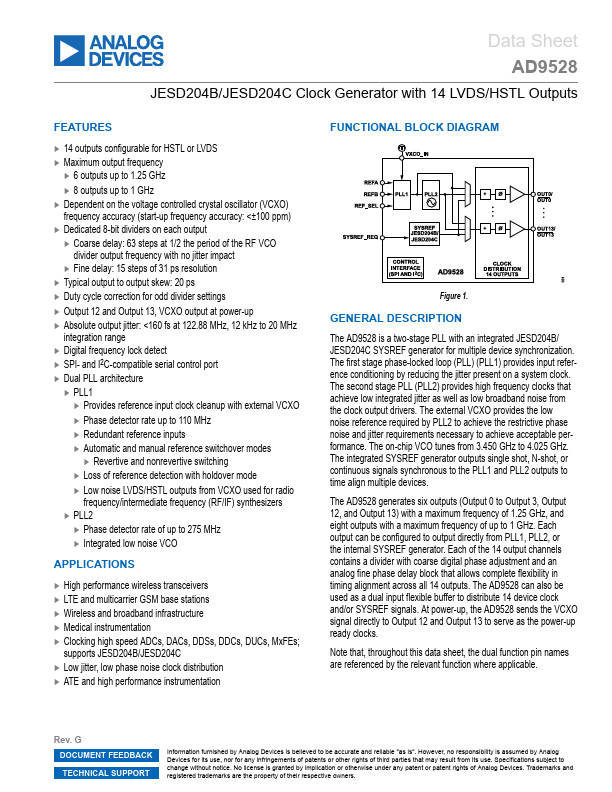

The AD9528 is a two-stage PLL with an integrated JESD204B/ JESD204C SYSREF generator for multiple device synchronization. The first stage phase-locked loop (PLL) (PLL1) provides input reference conditioning by reducing the jitter present o.

- 14 outputs configurable for HSTL or LVDS

- Maximum output frequency

- 6 outputs up to 1.25 GHz

- 8 outputs up to 1 GHz

- Dependent on the voltage controlled crystal oscillator (VCXO) frequency accuracy (start-up frequency accuracy: <±100 ppm)

- Dedicated 8-bit dividers on each output

- Coarse delay: 63 steps at 1/2 the period of the RF VCO divider output frequency with no jitter impact

- Fine delay: 15 steps of 31 ps resolution

- Typical output to output skew: 20 ps

- Duty cycle correction for odd divider settings