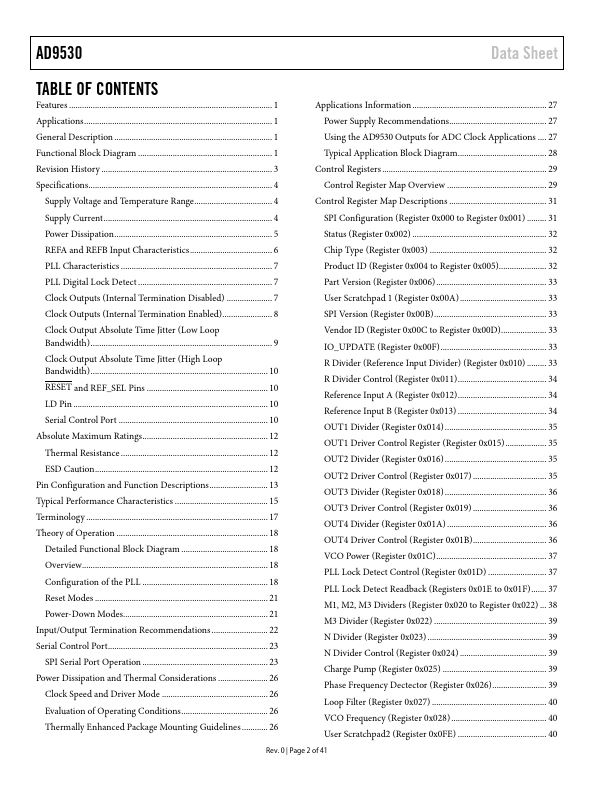

Datasheet Summary

Data Sheet

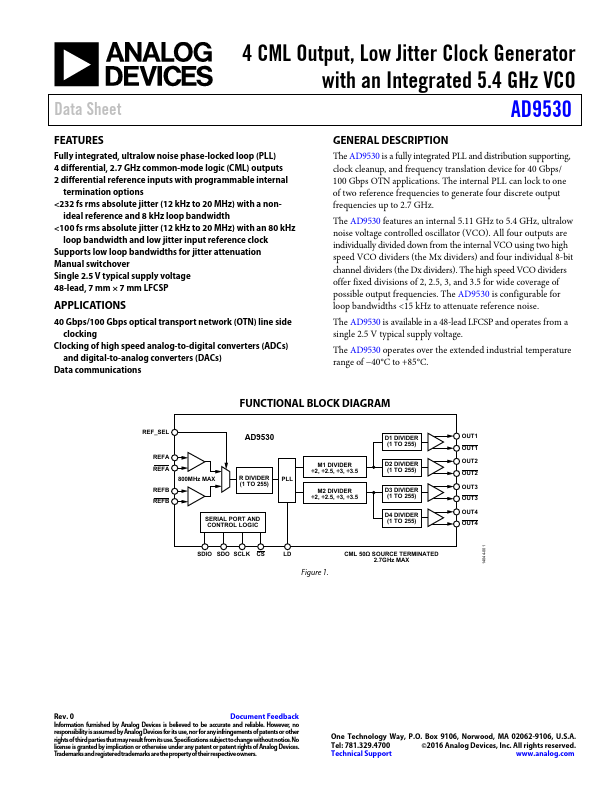

4 CML Output, Low Jitter Clock Generator with an Integrated 5.4 GHz VCO AD9530

Features

Fully integrated, ultralow noise phase-locked loop (PLL) 4 differential, 2.7 GHz mon-mode logic (CML) outputs 2 differential reference inputs with programmable internal termination options <232 fs rms absolute jitter (12 kHz to 20 MHz) with a non- ideal reference and 8 kHz loop bandwidth <100 fs rms absolute jitter (12 kHz to 20 MHz) with an 80 kHz loop bandwidth and low jitter input reference clock Supports low loop bandwidths for jitter attenuation Manual switchover Single 2.5 V typical supply voltage 48-lead, 7 mm × 7 mm LFCSP

APPLICATIONS

40 Gbps/100 Gbps optical transport network...