AD9548

Overview

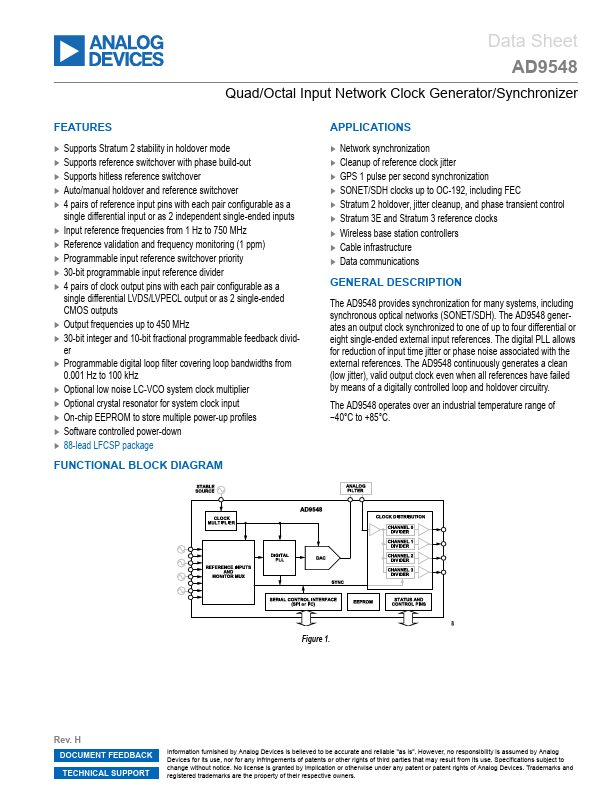

The AD9548 provides synchronization for many systems, including synchronous optical networks (SONET/SDH). The AD9548 generates an output clock synchronized to one of up to four differential or eight single-ended external input references.

- Supports Stratum 2 stability in holdover mode

- Supports reference switchover with phase build-out

- Supports hitless reference switchover

- Auto/manual holdover and reference switchover

- 4 pairs of reference input pins with each pair configurable as a single differential input or as 2 independent single-ended inputs

- Input reference frequencies from 1 Hz to 750 MHz

- Reference validation and frequency monitoring (1 ppm)

- Programmable input reference switchover priority

- 30-bit programmable input reference divider

- 4 pairs of clock output pins with each pair configurable as a single differential LVDS/LVPECL output or as 2 single-ended CMOS outputs