AD9694S-CSL

FEATURES

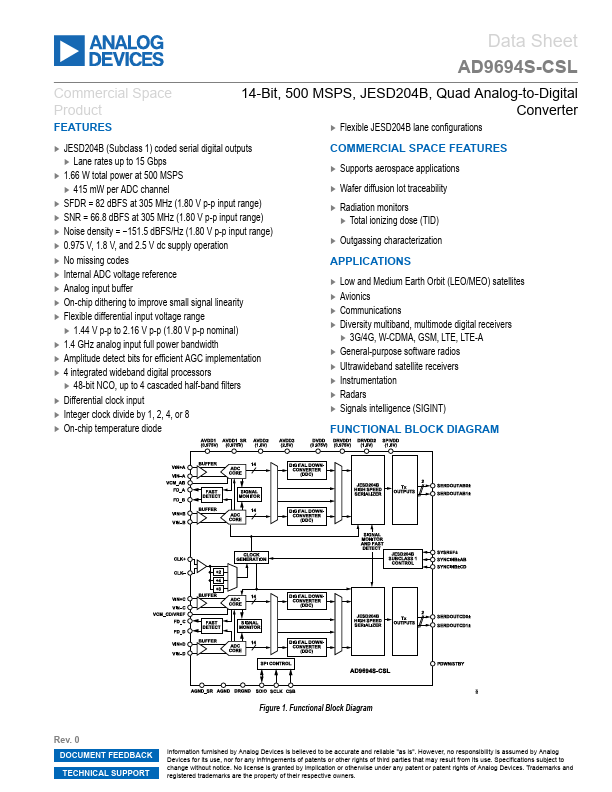

14-Bit, 500 MSPS, JESD204B, Quad Analog-to-Digital Converter

- Flexible JESD204B lane configurations

- JESD204B (Subclass 1) coded serial digital outputs

- Lane rates up to 15 Gbps

- 1.66 W total power at 500 MSPS

- 415 m W per ADC channel

- SFDR = 82 d BFS at 305 MHz (1.80 V p-p input range)

- SNR = 66.8 d BFS at 305 MHz (1.80 V p-p input range)

- Noise density =

- 151.5 d BFS/Hz (1.80 V p-p input range)

- 0.975 V, 1.8 V, and 2.5 V dc supply operation

- No missing codes

- Internal ADC voltage reference

- Analog input buffer

- On-chip dithering to improve small signal linearity

- Flexible differential input voltage range

- 1.44 V p-p to 2.16 V p-p (1.80 V p-p nominal)

- 1.4 GHz analog input full power bandwidth

- Amplitude detect bits for efficient AGC implementation

- 4 integrated wideband digital processors

- 48-bit NCO, up to 4 cascaded half-band filters

- Differential clock input

- Integer clock divide by 1, 2, 4, or 8

- On-chip temperature diode

MERCIAL SPACE FEATURES

-...