AD9852

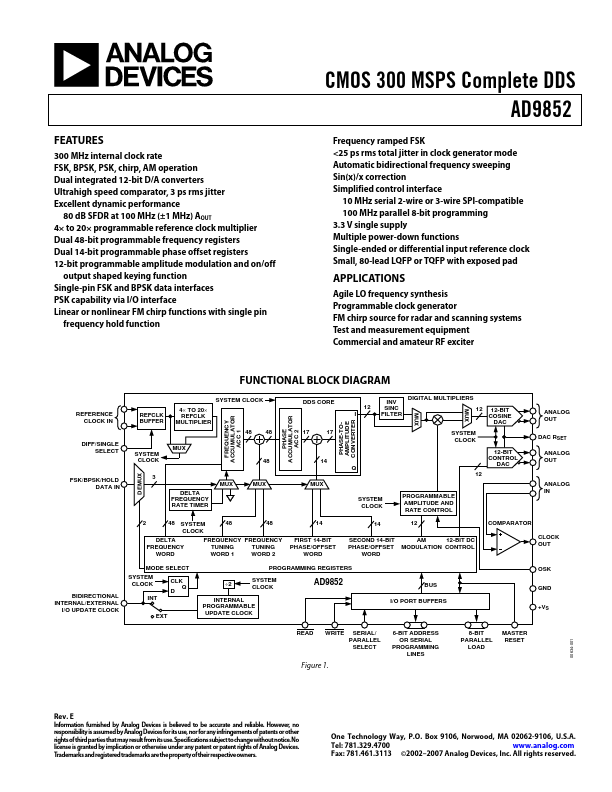

AD9852 is CMOS 300 MHz Complete-DDS manufactured by Analog Devices.

FEATURES

300 MHz internal clock rate FSK, BPSK, PSK, chirp, AM operation Dual integrated 12-bit D/A converters Ultrahigh speed parator, 3 ps rms jitter Excellent dynamic performance

80 d B SFDR at 100 MHz (±1 MHz) AOUT 4× to 20× programmable reference clock multiplier Dual 48-bit programmable frequency registers Dual 14-bit programmable phase offset registers 12-bit programmable amplitude modulation and on/off output shaped keying function Single-pin FSK and BPSK data interfaces PSK capability via I/O interface Linear or nonlinear FM chirp functions with single pin frequency hold function

CMOS 300 MSPS plete DDS

Frequency ramped FSK <25 ps rms total jitter in clock generator mode Automatic bidirectional frequency sweeping Sin(x)/x correction Simplified control interface

10 MHz serial 2-wire or 3-wire SPI-patible 100 MHz parallel 8-bit programming 3.3 V single supply Multiple power-down functions Single-ended or differential input reference clock Small, 80-lead LQFP...