AD9854

AD9854 is CMOS 300MSPS Quadrature Complete DDS manufactured by Analog Devices.

FEATURES

300 MHz internal clock rate FSK, BPSK, PSK, chirp, AM operation Dual integrated 12-bit digital-to-analog converters (DACs) Ultrahigh speed parator, 3 ps rms jitter Excellent dynamic performance

80 d B SFDR at 100 MHz (±1 MHz) AOUT 4× to 20× programmable reference clock multiplier Dual 48-bit programmable frequency registers Dual 14-bit programmable phase offset registers 12-bit programmable amplitude modulation and on/off output shaped keying function Single-pin FSK and BPSK data interfaces PSK capability via input/output interface Linear or nonlinear FM chirp functions with single-pin frequency hold function Frequency-ramped FSK <25 ps rms total jitter in clock generator mode

Automatic bidirectional frequency sweeping Sin(x)/x correction Simplified control interfaces

10 MHz serial 2- or 3-wire SPI patible 100 MHz parallel 8-bit programming 3.3 V single supply Multiple power-down functions Single-ended or differential input reference clock Small, 80-lead LQFP or TQFP with exposed pad

APPLICATIONS

Agile, quadrature LO frequency synthesis Programmable clock generators FM chirp source for radar and scanning systems Test and measurement equipment mercial and amateur RF exciters

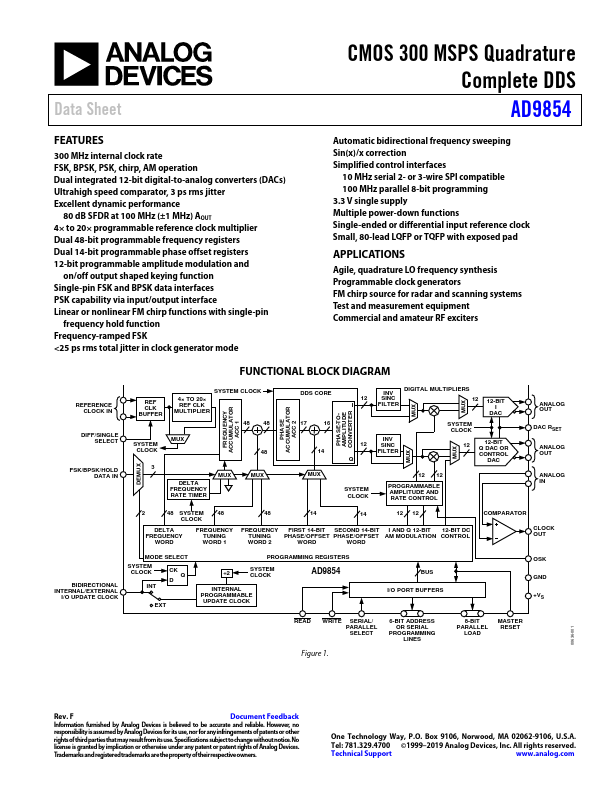

FUNCTIONAL BLOCK DIAGRAM

REFERENCE CLOCK IN

DIFF/SINGLE SELECT

FSK/BPSK/HOLD DATA IN

REF CLK BUFFER

SYSTEM CLOCK

4× TO 20× REF CLK MULTIPLIER

48 48

SYSTEM

CLOCK

DEMUX

DELTA FREQUENCY RATE TIMER

FREQUENCY ACCUMULATOR

ACC 1 PHASE ACCUMULATOR ACC 2 PHASE-TOAMPLITUDE CONVERTER

DDS CORE

14 MUX

12 I

12 Q

INV DIGITAL MULTIPLIERS

SINC

FILTER

12-BIT I

INV SINC...