ADSP-21061

features

KEY FEATURES

- PROCESSOR CORE

50 MIPS, 20 ns instruction rate, single-cycle instruction execution

120 MFLOPS peak, 80 MFLOPS sustained performance mercial Grade

SHARC DSP Microputer

ADSP-21061/ADSP-21061L

Dual data address generators with modulo and bit-reverse addressing

Efficient program sequencing with zero-overhead looping: single-cycle loop setup

IEEE JTAG Standard 1149.1 test access port and on-chip emulation

32-bit single-precision and 40-bit extended-precision IEEE floating-point data formats or 32-bit fixed-point data format

240-lead MQFP package, thermally enhanced MQFP, 225-ball plastic ball grid array (PBGA)

Lead (Pb) free packages. For more information, see Ordering Guide on Page 52.

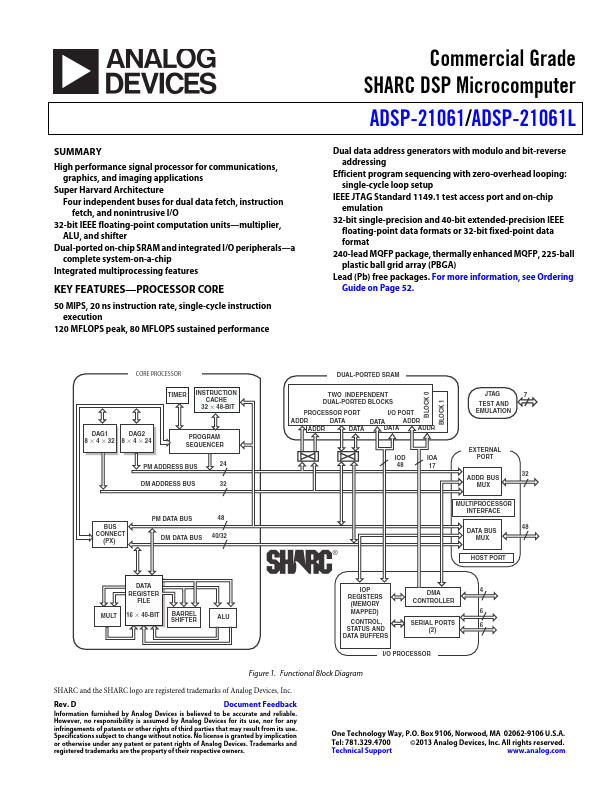

CORE PROCESSOR

TIMER

INSTRUCTION

CACHE 32 ϫ 48-BIT

DAG1

DAG2

8 ϫ 4 ϫ 32 8 ϫ 4 ϫ 24

PROGRAM SEQUENCER

PM ADDRESS BUS DM ADDRESS BUS

24 32

BUS CONNECT

(PX)

PM DATA BUS

DM DATA BUS 40/32

DUAL-PORTED SRAM

TWO INDEPENDENT DUAL-PORTED BLOCKS

PROCESSOR PORT

I/O...