ADSP-21065L

FEATURES

66 MIPS, 198 MFLOPS Peak, 132 MFLOPS Sustained Performance User-Configurable 544 Kbits On-Chip SRAM Memory Two External Port, DMA Channels and Eight Serial Port, DMA Channels

DSP Microputer ADSP-21065L

SDRAM Controller for Glueless Interface to Low Cost External Memory (@ 66 MHz) 64M Words External Address Range 12 Programmable I/O Pins and Two Timers with Event Capture Options Code-patible with ADSP-2106x Family 208-Lead MQFP or 196-Ball Mini-BGA Package 3.3 Volt Operation

Flexible Data Formats and 40-Bit Extended Precision 32-Bit Single-Precision and 40-Bit Extended-Precision IEEE Floating-Point Data Formats 32-Bit Fixed-Point Data Format, Integer and Fractional, with Dual 80-Bit Accumulators Parallel putations Single-Cycle Multiply and ALU Operations in Parallel with Dual Memory Read/Writes and Instruction Fetch Multiply with Add and Subtract for Accelerated FFT Butterfly putation 1024-Point plex FFT Benchmark: 0.274 ms (18,221 Cycles)

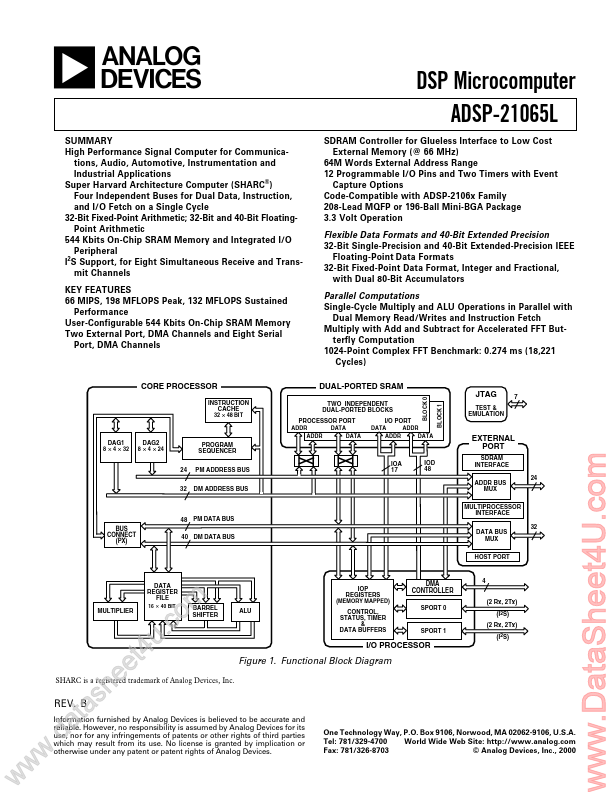

DUAL-PORTED SRAM

BLOCK 1

CORE...