ADSP-21571

ADSP-21571 is manufactured by Analog Devices.

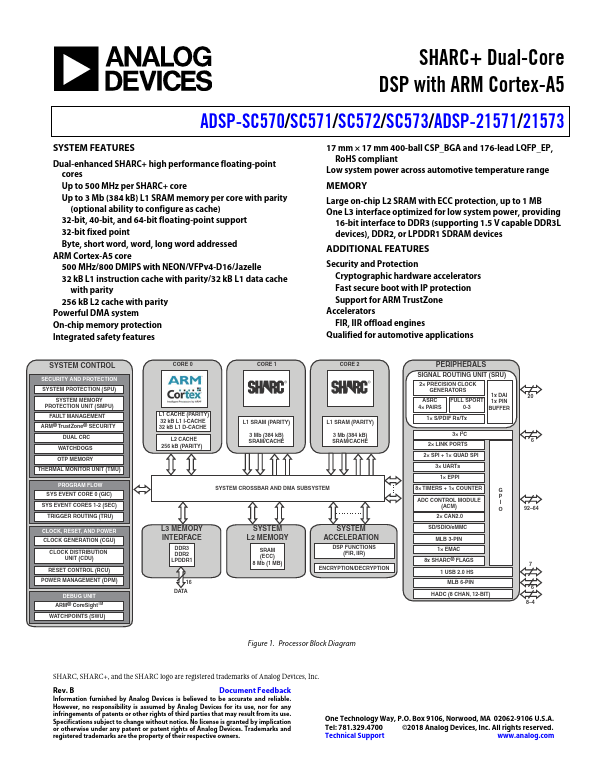

SHARC+ Dual-Core DSP with ARM Cortex-A5

ADSP-SC570/SC571/SC572/SC573/ADSP-21571/21573

SYSTEM Features

Dual-enhanced SHARC+ high performance floating-point cores Up to 500 MHz per SHARC+ core Up to 3 Mb (384 kB) L1 SRAM memory per core with parity (optional ability to configure as cache) 32-bit, 40-bit, and 64-bit floating-point support 32-bit fixed point Byte, short word, word, long word addressed

ARM Cortex-A5 core 500 MHz/800 DMIPS with NEON/VFPv4-D16/Jazelle 32 kB L1 instruction cache with parity/32 kB L1 data cache with parity 256 kB L2 cache with parity

Powerful DMA system On-chip memory protection Integrated safety Features

17 mm × 17 mm 400-ball CSP_BGA and 176-lead LQFP_EP, RoHS...