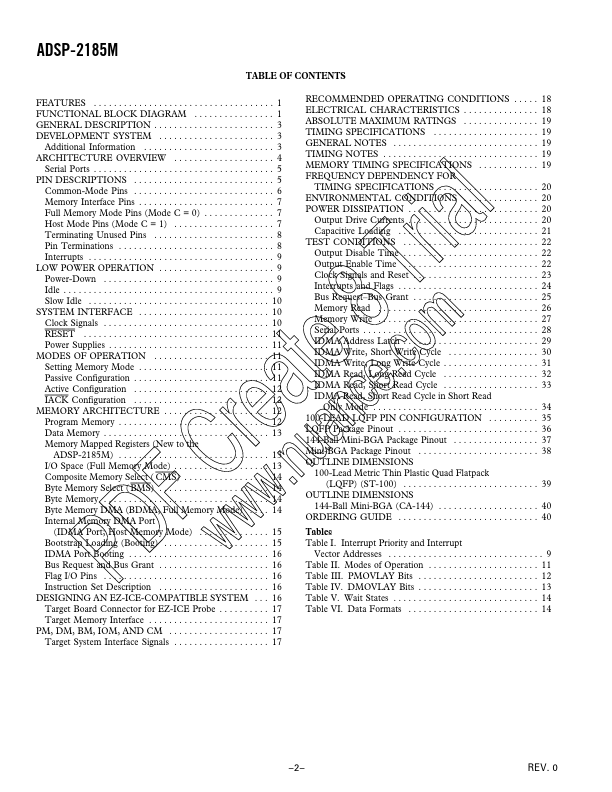

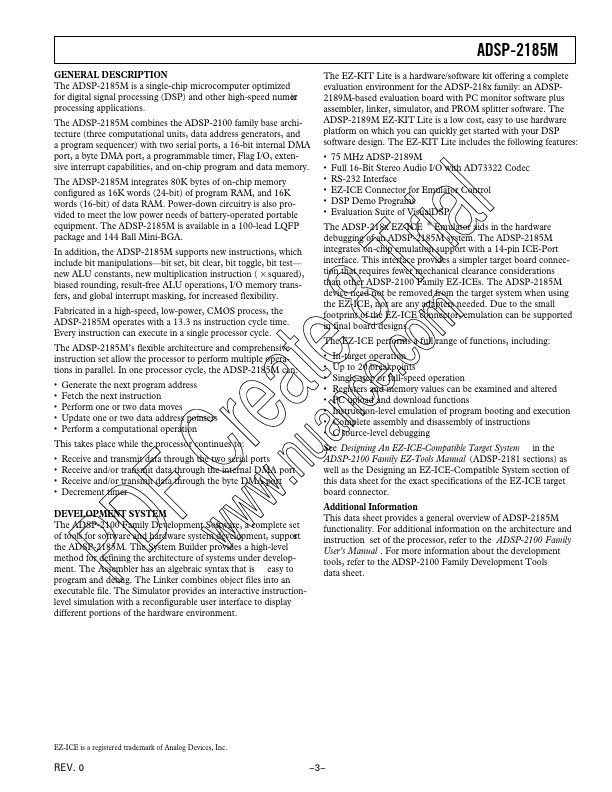

Datasheet Summary

a

Features

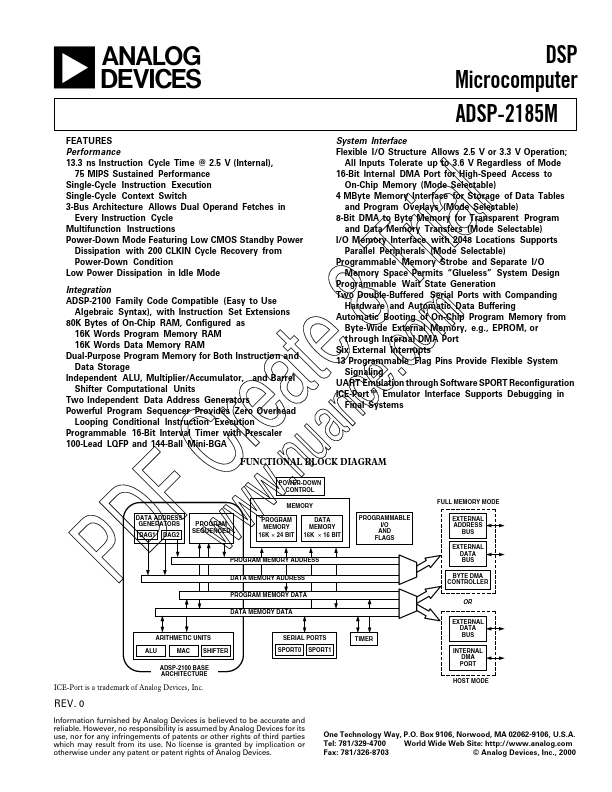

Performance 13.3 ns Instruction Cycle Time @ 2.5 V (Internal), 75 MIPS Sustained Performance Single-Cycle Instruction Execution Single-Cycle Context Switch 3-Bus Architecture Allows Dual Operand Fetches in Every Instruction Cycle Multifunction Instructions Power-Down Mode Featuring Low CMOS Standby Power Dissipation with 200 CLKIN Cycle Recovery from Power-Down Condition Low Power Dissipation in Idle Mode

DSP Microputer ADSP-2185M

System Interface Flexible I/O Structure Allows 2.5 V or 3.3 V Operation; All Inputs Tolerate up to 3.6 V Regardless of Mode 16-Bit Internal DMA Port for High-Speed Access to On-Chip Memory (Mode Selectable) 4 MByte Memory Interface for Storage of...