ADSP-2196

ADSP-2196 is DSP Microcomputer manufactured by Analog Devices.

35(/,0,1$5< 7(&+1,&$/ '$7$ a U 4 t w w m o .c e e Preliminary Technical Data h S a at .D w

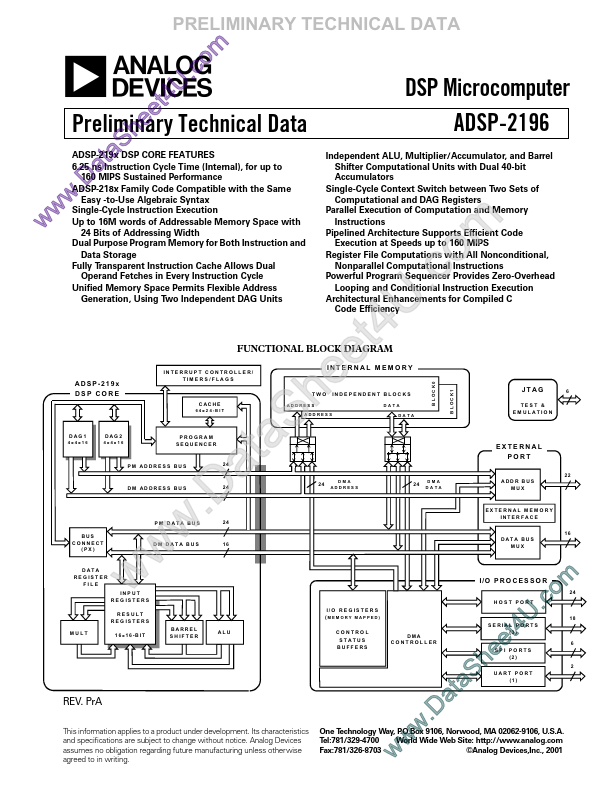

ADSP-219x DSP CORE Features

6.25 ns Instruction Cycle Time (Internal), for up to 160 MIPS Sustained Performance ADSP-218x Family Code patible with the Same Easy -to-Use Algebraic Syntax Single-Cycle Instruction Execution Up to 16M words of Addressable Memory Space with 24 Bits of Addressing Width Dual Purpose Program Memory for Both Instruction and Data Storage Fully Transparent Instruction Cache Allows Dual Operand Fetches in Every Instruction Cycle Unified Memory Space Permits Flexible Address Generation, Using Two Independent DAG Units

DSP Microputer ADSP-2196

Independent ALU,...