| Part | ADSP-SC596 |

|---|---|

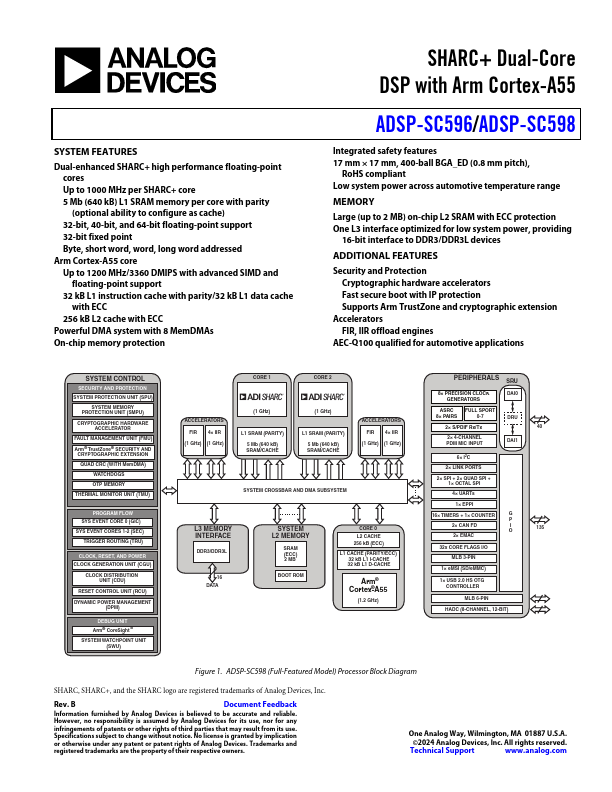

| Description | SHARC+ Dual-Core DSP |

| Manufacturer | Analog Devices |

| Size | 4.51 MB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| ACM8628M | ACME | Digital Input Amplifier Built-in DSP |

| DU561 | MVSILICON | High-performance Audio DSP |

| RK2118M | Rockchip | high-performance triple-core HiFi4 DSP processor |