ADSP-SC598

Key Features

- B Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable

- Specifications subject to change without notice

- No license is granted by implication or otherwise under any patent or patent rights of Analog Devices

- Trademarks and registered trademarks are the property of their respective owners

- One Analog Way, Wilmington, MA 01887 U.S.A

- ©2024 Analog Devices, Inc

- All rights reserved

- Technical Support .analog

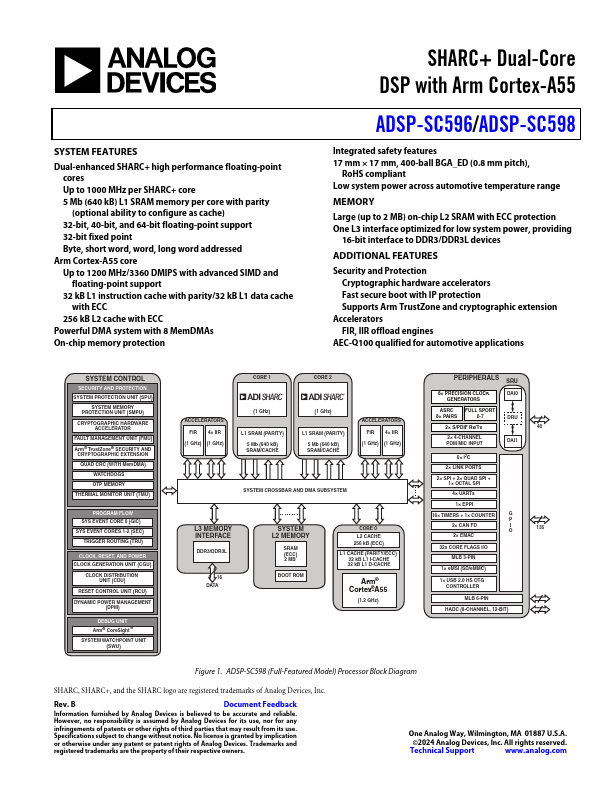

- ADSP-SC596/ADSP-SC598 ARM Cortex-A55 Processor