ADSP21msp59

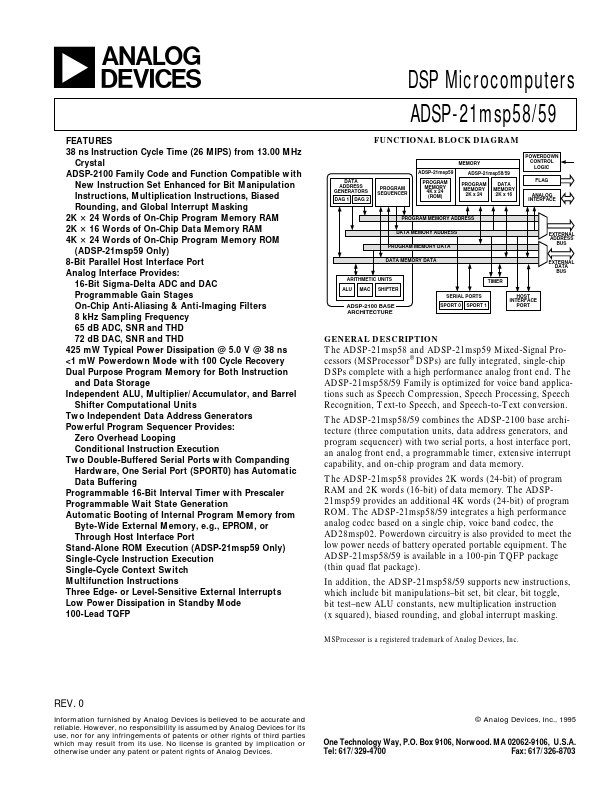

ADSP21msp59 is (ADSP21msp58 / ADSP21msp59) DSP Microcomputers manufactured by Analog Devices.

- Part of the ADSP-21msp58 comparator family.

- Part of the ADSP-21msp58 comparator family.

a

Features

38 ns Instruction Cycle Time (26 MIPS) from 13.00 MHz Crystal ADSP-2100 Family Code and Function patible with New Instruction Set Enhanced for Bit Manipulation Instructions, Multiplication Instructions, Biased Rounding, and Global Interrupt Masking 2K ؋ 24 Words of On-Chip Program Memory RAM 2K ؋ 16 Words of On-Chip Data Memory RAM 4K ؋ 24 Words of On-Chip Program Memory ROM (ADSP-21msp59 Only) 8-Bit Parallel Host Interface Port Analog Interface Provides: 16-Bit Sigma-Delta ADC and DAC Programmable Gain Stages On-Chip Anti-Aliasing & Anti-Imaging Filters 8 kHz Sampling Frequency 65 dB ADC, SNR and THD 72 dB DAC, SNR and THD 425 mW Typical Power Dissipation @ 5.0 V @ 38 ns <1...