Datasheet Summary

16-nm 16 x 56 Gb/s PAM-4 Duplex PHY

Data Sheet

Overview

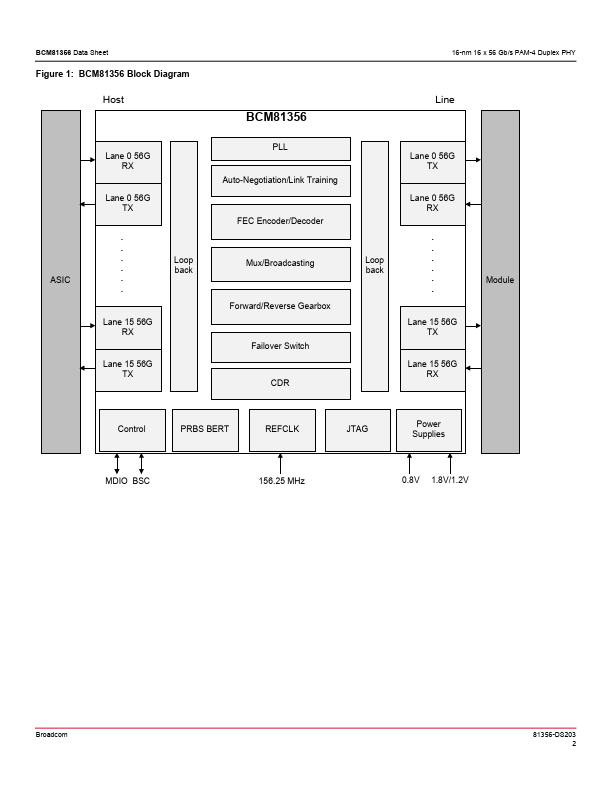

The Broad® BCM81356 is a single-chip 16 × 56 Gb/s full-duplex PHY. It supports both the PAM-4 and NRZ data formats. It supports various operation modes, such as Retimer, Forward, and Reverse Gearbox modes. It also supports 10G, 25G, 40G, 50G, 100G, 200G, and 400G linecard applications.

On-chip clock synthesis is performed by a low-cost reference clock through high-frequency, low-jitter phaselocked loops (PLLs).

The BCM81356 is fabricated in advanced low-power 16-nm CMOS technology.

The BCM81356 is available in a 23 mm × 23 mm, 0.8-mm pitch, 729-ball BGA, RoHS-pliant package.

Applications

- ASIC-to-module interface 16...