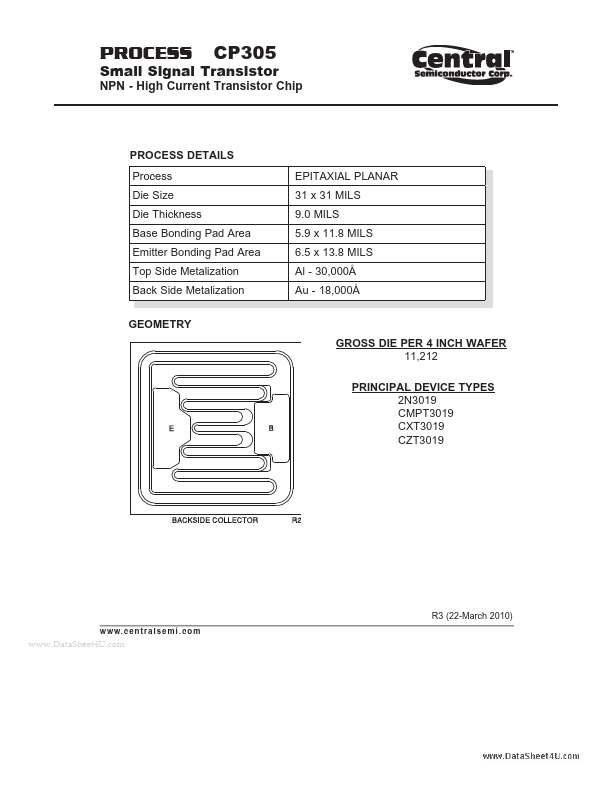

CP305

CP305 is Small Signal Transistor NPN - High Current Transistor Chip manufactured by Central Semiconductor.

PROCESS

Small Signal Transistor

- High Current Transistor Chip

PROCESS DETAILS Process Die Size Die Thickness Base Bonding Pad Area Emitter Bonding Pad Area Top Side Metalization Back Side Metalization GEOMETRY GROSS DIE PER 4 INCH WAFER 11,212 PRINCIPAL DEVICE TYPES 2N3019 CMPT3019 CXT3019 CZT3019 EPITAXIAL PLANAR 31 x 31 MILS 9.0 MILS 5.9 x 11.8 MILS 6.5 x 13.8 MILS Al

- 30,000Å Au

- 18,000Å

R3 (22-March 2010) w w w. c e n t r a l s e m i . c o m

..

PROCESS

Typical Electrical Characteristics

R3 (22-March 2010) w w w. c e n t r a l s e m i . c o...