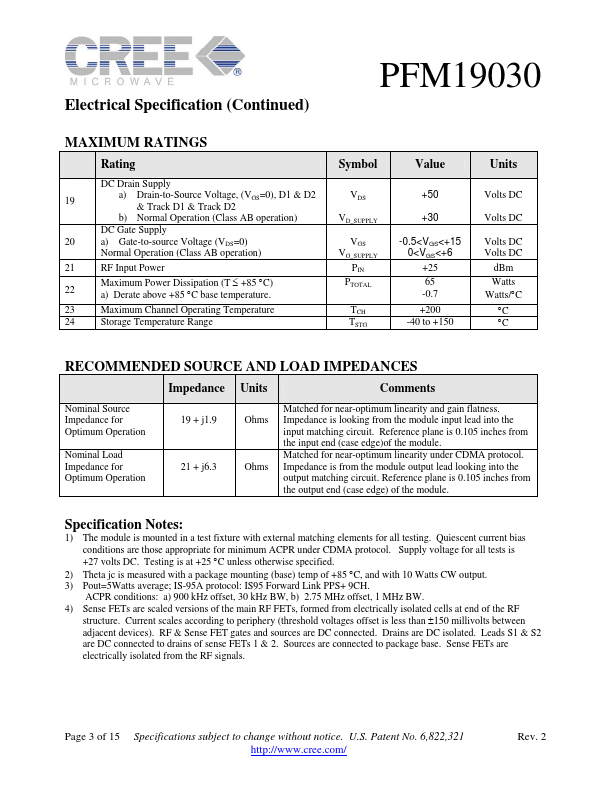

PFM19030 Datasheet Text

w

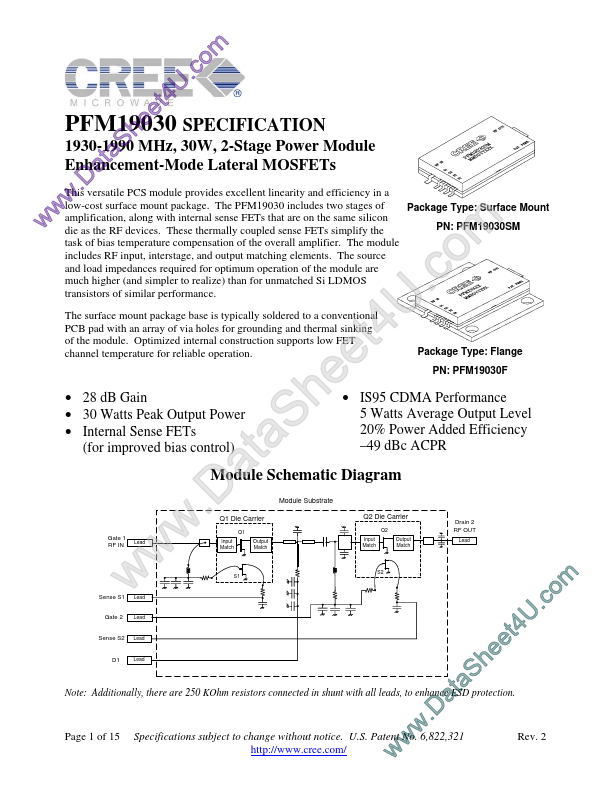

U 4 t e e SPECIFICATION PFM19030 h S MHz, 30W, 2-Stage Power Module 1930-1990 a Enhancement-Mode Lateral MOSFETs at .D This PCS module provides excellent linearity and efficiency in a w versatile low-cost surface mount package. The PFM19030 includes two stages of wamplification, along with internal sense FETs that are on the same silicon die as the RF devices. These thermally coupled sense FETs simplify the task of bias temperature pensation of the overall amplifier. The module includes RF input, interstage, and output matching elements. The source and load impedances required for optimum operation of the module are much higher (and simpler to realize) than for unmatched Si LDMOS transistors of similar performance. The surface mount package base is typically soldered to a conventional PCB pad with an array of via holes for grounding and thermal sinking of the module. Optimized internal construction supports low FET channel temperature for reliable operation. m o .c

Package Type: Surface Mount PN: PFM19030SM

- 28 dB Gain

- 30 Watts Peak Output Power

- Internal Sense FETs (for improved bias control)

Gate 1 RF IN

Lead

Sense S1 Gate 2 w

Lead Lead Lead Lead w

.D w

Input Match S1

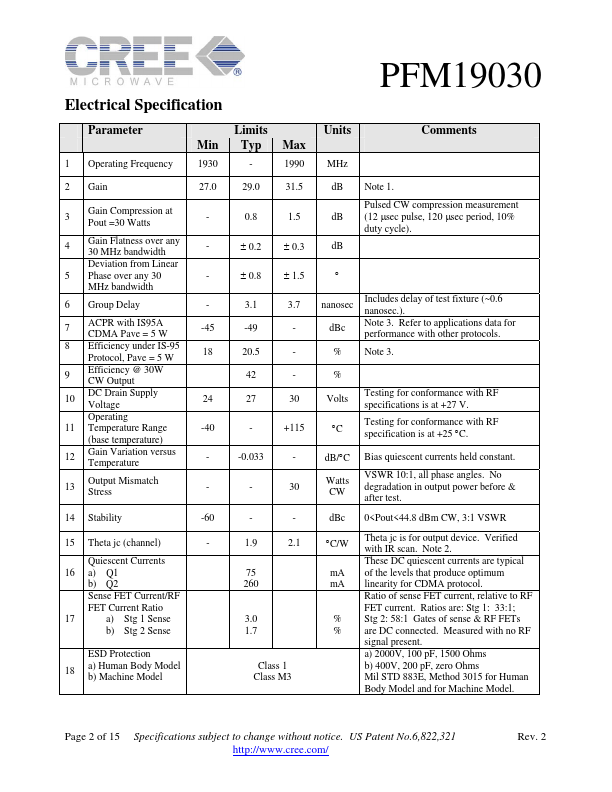

Module Schematic Diagram

Module Substrate Q2 Die Carrier

Q2 Output Match Input Match Output Match t a

S a e h t e

U 4

.c m o

Package Type: Flange PN: PFM19030F

- IS95 CDMA Performance 5 Watts Average Output Level 20% Power Added Efficiency

- 49 dBc ACPR

Q1 Die Carrier

Q1

Drain 2 RF OUT

Lead

S2

Sense S2

S a Note: Additionally, there are 250 KOhm resistors connected in shunt with all leads, to enhance ESD at protection. .D w Page 1 of 15 Specifications subject to change without notice. U.S. Patent No. 6,822,321 Rev. 2 w http://.cree./ w

D1 e e h

U 4 t m o...