CY28343 Overview

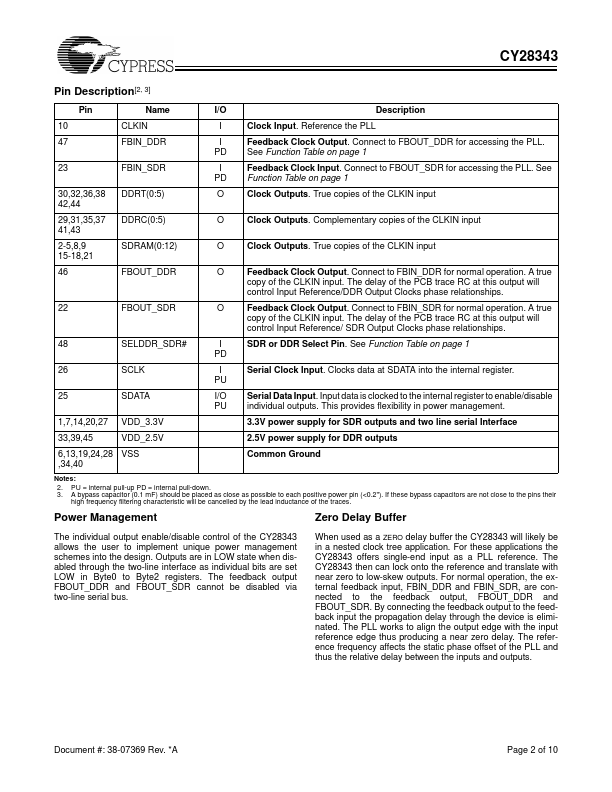

Reference the PLL Feedback Clock Output. Connect to FBOUT_DDR for accessing the PLL. See Function Table on page 1 Feedback Clock Input.

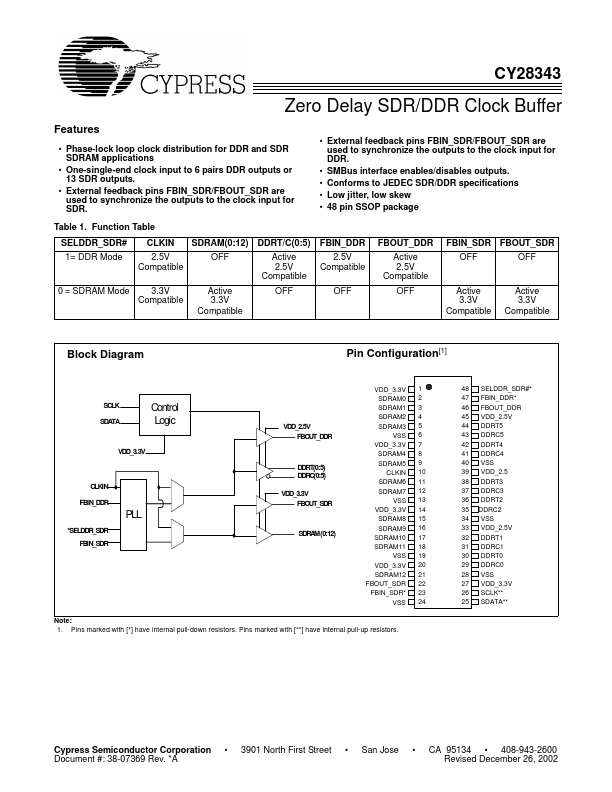

CY28343 Key Features

- Phase-lock loop clock distribution for DDR and SDR SDRAM

CY28343 Applications

- One-single-end clock input to 6 pairs DDR outputs or 13 SDR outputs