CY28408

CY28408 is Clock Synthesizer manufactured by Cypress.

..

Clock Synthesizer with Differential CPU Outputs

Features

- patible to Intel® CK 408 Mobile Clock Synthesizer

- Support Intel P4 and Brookdale CPU

- Specifications

- 3.3V power supply

- Three differential CPU clocks

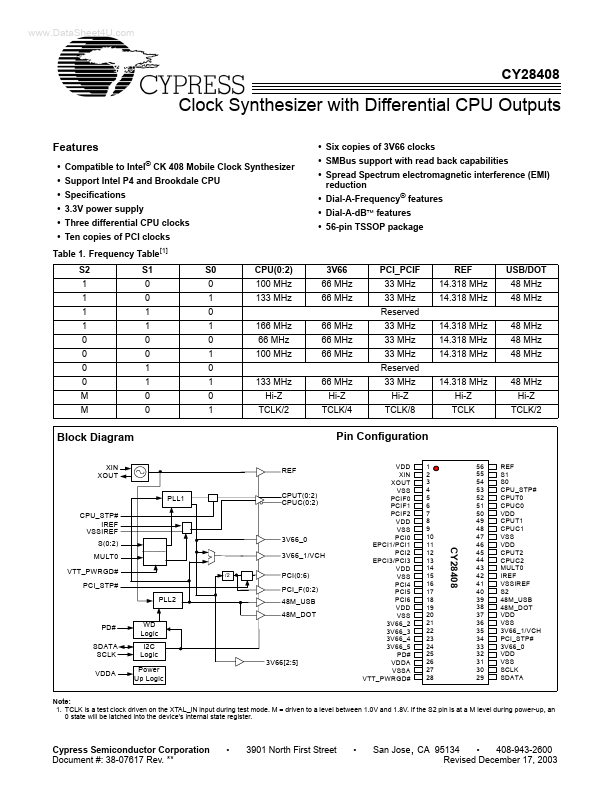

- Ten copies of PCI clocks Table 1. Frequency Table[1] S2 1 1 1 1 0 0 0 0 M M S1 0 0 1 1 0 0 1 1 0 0 S0 0 1 0 1 0 1 0 1 0 1 133 MHz Hi-Z TCLK/2 66 MHz Hi-Z TCLK/4 166 MHz 66 MHz 100 MHz 66 MHz 66 MHz 66 MHz CPU(0:2) 100 MHz 133 MHz 3V66 66 MHz 66 MHz PCI_PCIF 33 MHz 33 MHz Reserved 33 MHz 33 MHz 33 MHz Reserved 33 MHz Hi-Z TCLK/8 14.318 MHz Hi-Z TCLK 48 MHz Hi-Z TCLK/2 14.318 MHz 14.318 MHz 14.318 MHz 48 MHz 48 MHz 48 MHz REF 14.318 MHz 14.318 MHz USB/DOT 48 MHz 48 MHz

- Six copies of 3V66 clocks

- SMBus support with read back capabilities

- Spread Spectrum electromagnetic interference (EMI) reduction

- Dial-A-Frequency® Features

- Dial-A-d B Features

- 56-pin TSSOP package

Block Diagram

XIN XOUT PLL1 CPU_STP# IREF VSSIREF S(0:2) MULT0 VTT_PWRGD# PCI_STP# PLL2 WD Logic I2C Logic Power Up Logic

/2

Pin Configuration

REF CPUT(0:2) CPUC(0:2)

VDD XIN XOUT VSS PCIF0 PCIF1 PCIF2 VDD VSS PCI0 EPCI1/PCI1 PCI2 EPCI3/PCI3 VDD VSS PCI4 PCI5 PCI6 VDD VSS 3V66_2 3V66_3 3V66_4 3V66_5 PD# VDDA VSSA VTT_PWRGD# 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 REF S1 S0 CPU_STP# CPUT0 CPUC0 VDD CPUT1 CPUC1 VSS VDD CPUT2 CPUC2 MULT0 IREF VSSIREF S2 48M_USB 48M_DOT VDD VSS 3V66_1/VCH PCI_STP# 3V66_0 VDD VSS SCLK SDATA

3V66_0 3V66_1/VCH PCI(0:6) PCI_F(0:2) 48M_USB 48M_DOT

PD# SDATA SCLK VDDA

3V66[2:5]

Note: 1. TCLK is a test clock driven on the XTAL_IN input during test mode. M = driven to a level between 1.0V and 1.8V. If the S2 pin is at a M level during power-up, an 0 state will be latched into the device’s internal state register.

Cypress Semiconductor Corporation Document #: 38-07617 Rev.

- -

- 3901 North First...