CY6264 Description

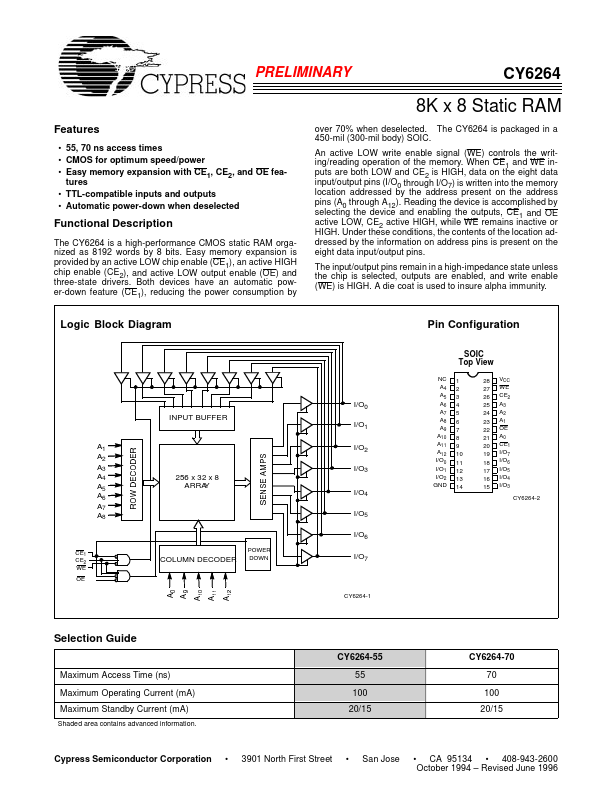

The CY6264 is a high-performance CMOS static RAM organized as 8192 words by 8 bits. Easy memory expansion is provided by an active LOW chip enable (CE1), an active HIGH chip enable (CE2), and active LOW output enable (OE) and three-state drivers. Both devices have an automatic power-down.

CY6264 Key Features

- 55, 70 ns access times

- CMOS for optimum speed/power

- Easy memory expansion with CE1, CE2, and OE features

- TTL-patible inputs and outputs