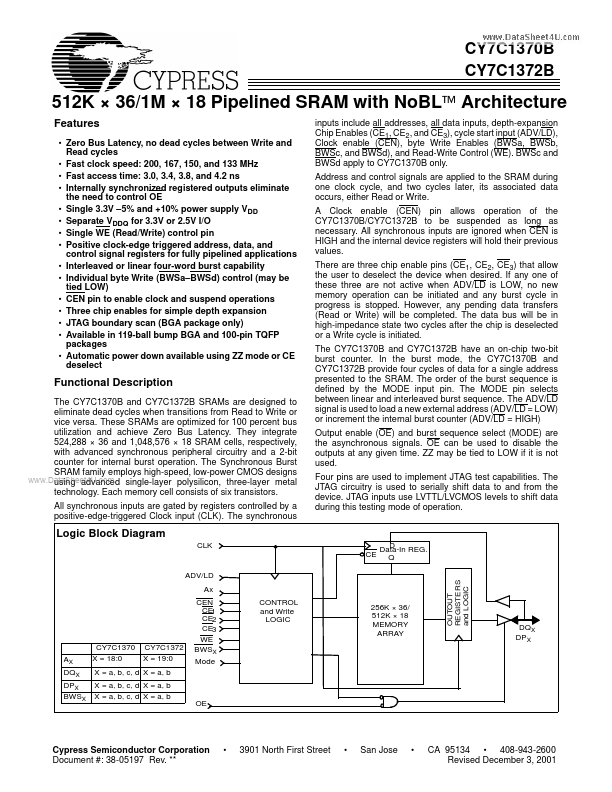

CY7C1370B

Key Features

- Zero Bus Latency, no dead cycles between Write and Read cycles

- Fast clock speed: 200, 167, 150, and 133 MHz

- Fast access time: 3.0, 3.4, 3.8, and 4.2 ns

- Internally synchronized registered outputs eliminate the need to control OE

- Single 3.3V -5% and +10% power supply VDD

- Separate VDDQ for 3.3V or 2.5V I/O

- Single WE (Read/Write) control pin

- Positive clock-edge triggered address, data, and control signal registers for fully pipelined applications

- Interleaved or linear four-word burst capability

- Individual byte Write (BWSa-BWSd) control (may be tied LOW)