CY7C1426AV18

CY7C1426AV18 is (CY7C14xxAV18) 36-Mbit QDR-II SRAM 4-Word Burst Architecture manufactured by Cypress.

- Part of the CY7C1413AV18 comparator family.

- Part of the CY7C1413AV18 comparator family.

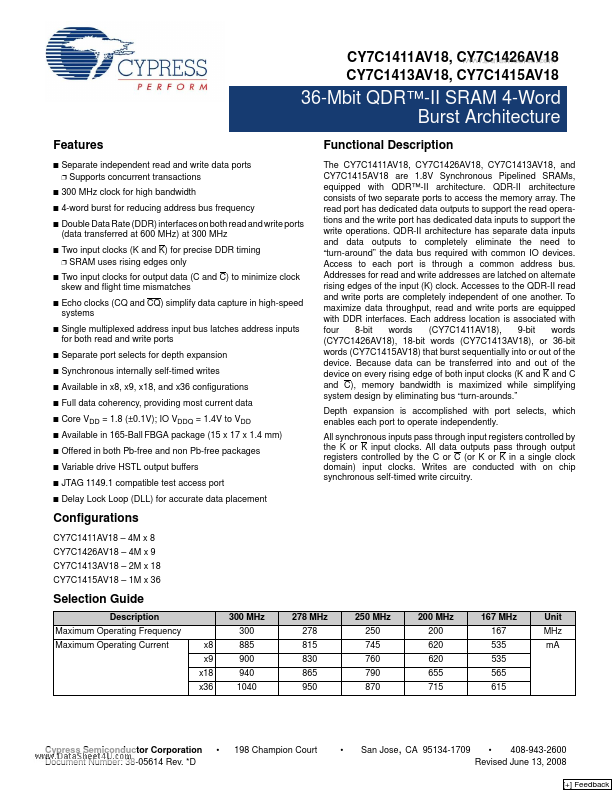

CY7C1411AV18, CY7C1426AV18 .. CY7C1413AV18, CY7C1415AV18

36-Mbit QDR™-II SRAM 4-Word Burst Architecture

Features

- Functional Description

The CY7C1411AV18, CY7C1426AV18, CY7C1413AV18, and CY7C1415AV18 are 1.8V Synchronous Pipelined SRAMs, equipped with QDR™-II architecture. QDR-II architecture consists of two separate ports to access the memory array. The read port has dedicated data outputs to support the read operations and the write port has dedicated data inputs to support the write operations. QDR-II architecture has separate data inputs and data outputs to pletely eliminate the need to “turn-around” the data bus required with mon IO devices. Access to each...