CY7C4265V

CY7C4265V is 32K/64Kx18 Low Voltage Deep Sync FIFOs manufactured by Cypress.

- Part of the CY7C4275V comparator family.

- Part of the CY7C4275V comparator family.

285V

CY7C4255V/CY7C4265V CY7C4275V/CY7C4285V

32K/64Kx18 Low Voltage Deep Sync FIFOs

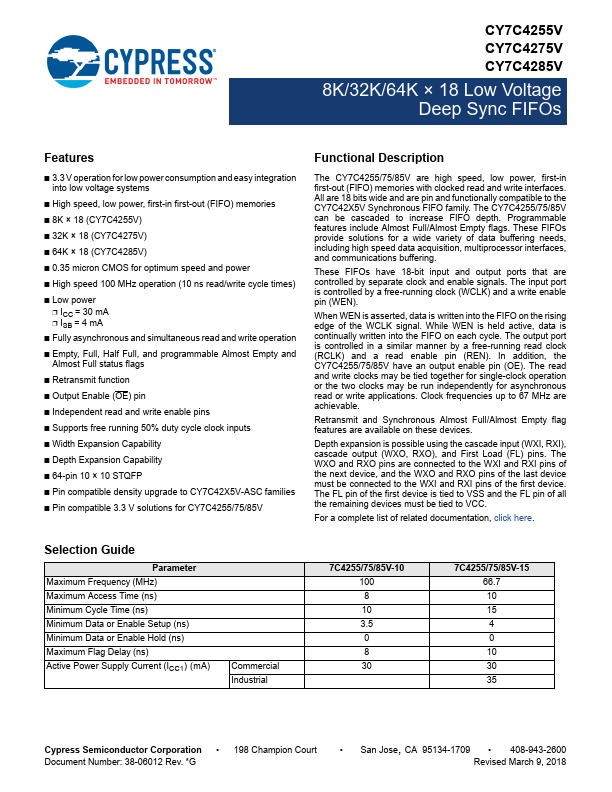

Features

- 3.3V operation for low power consumption and easy integration into low-voltage systems

- High-speed, low-power, first-in first-out (FIFO) memories

- 8K x 18 (CY7C4255V)

- 16K x 18 (CY7C4265V)

- 32K x 18 (CY7C4275V)

- 64K x 18 (CY7C4285V)

- 0.35 micron CMOS for optimum speed/power

- High-speed 100-MHz operation (10-ns read/write cycle times)

- Low power

- ICC = 30 m A

- ISB = 4 m A

- Fully asynchronous and simultaneous read and write operation

- Empty, Full, Half Full, and programmable Almost Empty and Almost Full status flags

- Retransmit function

- Output Enable (OE) pin

- Independent read and write enable pins

- Supports free-running 50% duty cycle clock inputs

- Width Expansion Capability

- Depth Expansion Capability

- 64-pin 10x10 STQFP

- Pin-patible density upgrade to CY7C42X5V-ASC families

- Pin-patible 3.3V solutions for CY7C4255/65/75/85

..

Functional Description

The CY7C4255/65/75/85V are high-speed, low-power, first-in first-out (FIFO) memories with clocked read and write interfaces. All are 18 bits wide and are pin/functionally patible to the CY7C42X5V Synchronous FIFO family. The CY7C4255/65/75/85V can be cascaded to increase FIFO depth. Programmable Features include Almost Full/Almost Empty flags. These FIFOs provide solutions for a wide variety of data buffering needs, including high-speed data acquisition, multiprocessor interfaces, and munications buffering. These FIFOs have 18-bit input and output ports that are controlled by separate clock and enable signals. The input port is controlled by a free-running clock (WCLK) and a write enable pin (WEN). When WEN is asserted, data is written into the FIFO on the rising edge of the WCLK signal. While WEN is held active, data is continually written into the FIFO on each cycle. The output port is controlled in a similar manner by a free-running read clock (RCLK) and a read enable pin...