W163

Description

Voltage on any pin with respect to GND Storage Temperature Operating Temperature Ambient Temperature under Bias Power Dissipation DC Parameter IDD VIL VIH VOL VOH IIL IIH Description Supply Current Input Low Voltage Input High Voltage Output Low Voltage Output High Voltage Input Low Current Input High Current IOL = 12 mA (-15) IOL = 8 mA (-5) IOL = 12 mA (-15) IOL = 8 mA (-5) VIN = 0V VIN = VDD 2.4 50 100 2.0 0.4 Test Condition Unloaded, 100 MHz Min Typ Max 40 0.8 Unit mA V V V V µA µA AC Parameter fIN fOUT tR tF tICLKR tICLKF tPD tSK tSKDD tD tLOCK tJC Description Input Fr.

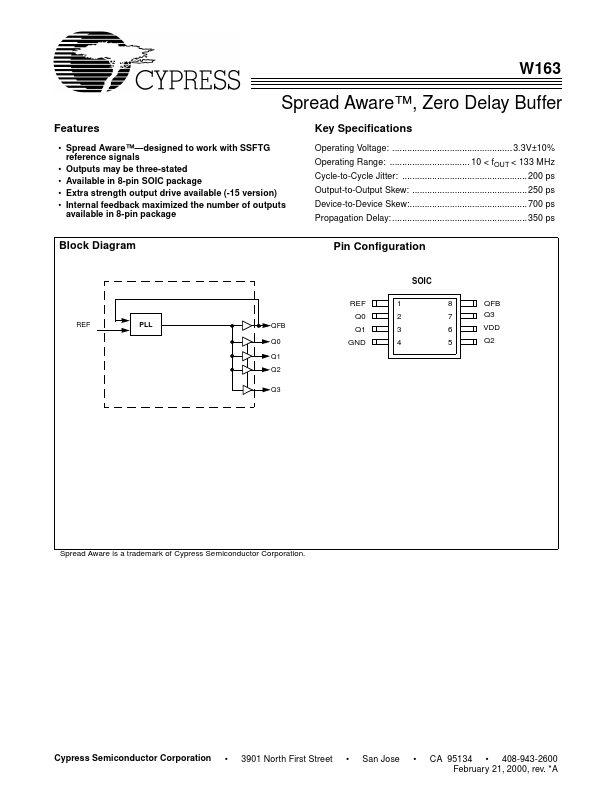

Key Features

- Spread Aware™-designed to work with SSFTG reference signals

- Outputs may be three-stated

- Available in 8-pin SOIC package

- Extra strength output drive available (-15 version)