CY7C4041KV13 Description

CY7C4021KV13/CY7C4041KV13 72-Mbit QDR™-IV HP SRAM 72-Mbit QDR™-IV HP SRAM.

CY7C4041KV13 Key Features

- 72-Mbit density (4M ×18, 2M ×36)

- Total Random Transaction Rate [1] of 1334 MT/s

- Maximum operating frequency of 667 MHz

- Read latency of 5.0 clock cycles and Write latency of 3.0 clock cycles

- Two-word burst on all accesses

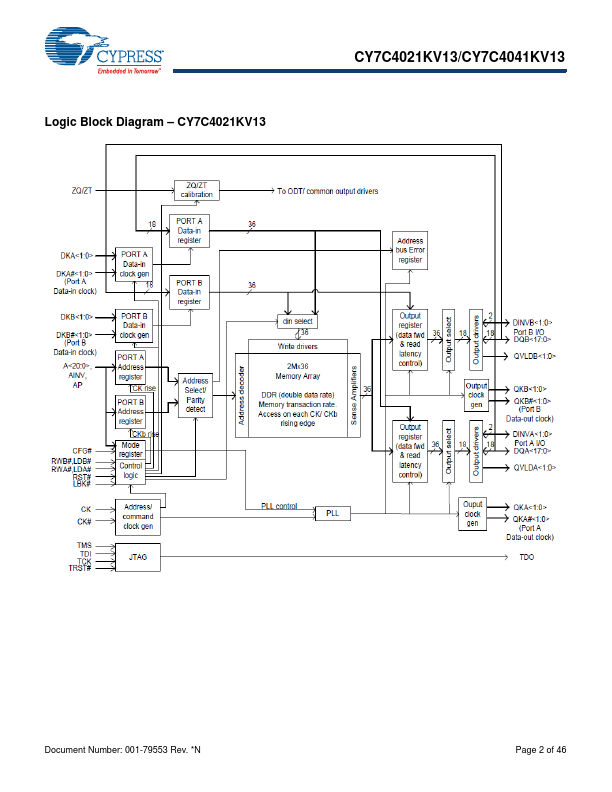

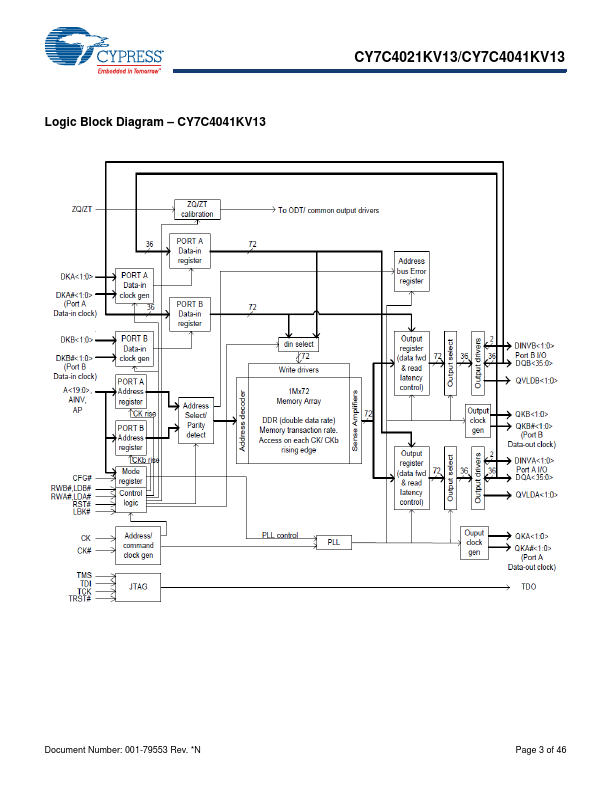

- Dual independent bi-directional data ports

- Double data rate (DDR) data ports

- Supports concurrent read/write transactions on both ports

- Single address port used to control both data ports

- DDR address signaling