Datasheet Summary

P-CHANNEL ENHANCEMENT MODE MOSFET

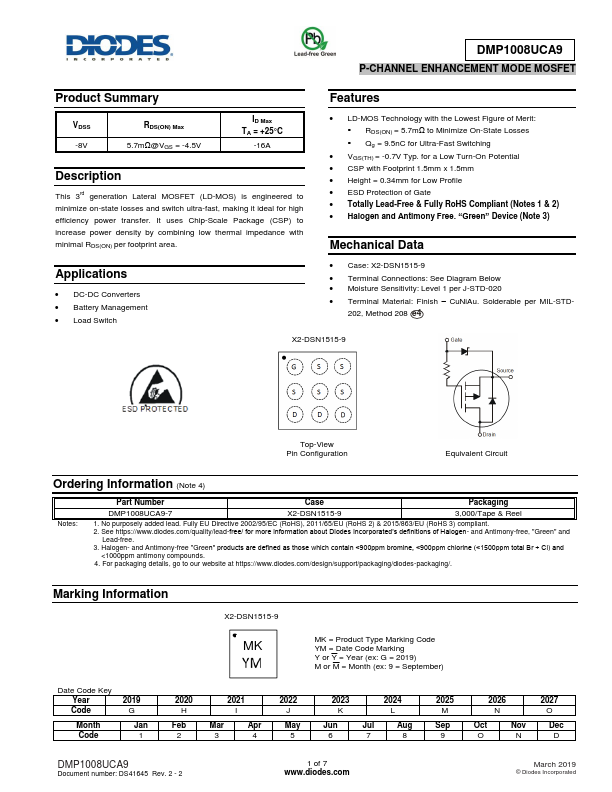

Product Summary

Features

VDSS -8V

RDS(ON) Max 5.7mΩ@VGS = -4.5V

ID Max TA = +25°C

-16A

Description

This 3rd generation Lateral MOSFET (LD-MOS) is engineered to minimize on-state losses and switch ultra-fast, making it ideal for high efficiency power transfer. It uses Chip-Scale Package (CSP) to increase power density by bining low thermal impedance with minimal RDS(ON) per footprint area.

- LD-MOS Technology with the Lowest Figure of Merit:

- RDS(ON) = 5.7mΩ to Minimize On-State Losses

- Qg = 9.5nC for Ultra-Fast Switching

- VGS(TH) = -0.7V Typ. for a Low Turn-On Potential

- CSP with Footprint 1.5mm x 1.5mm

- Height = 0.34mm for Low...