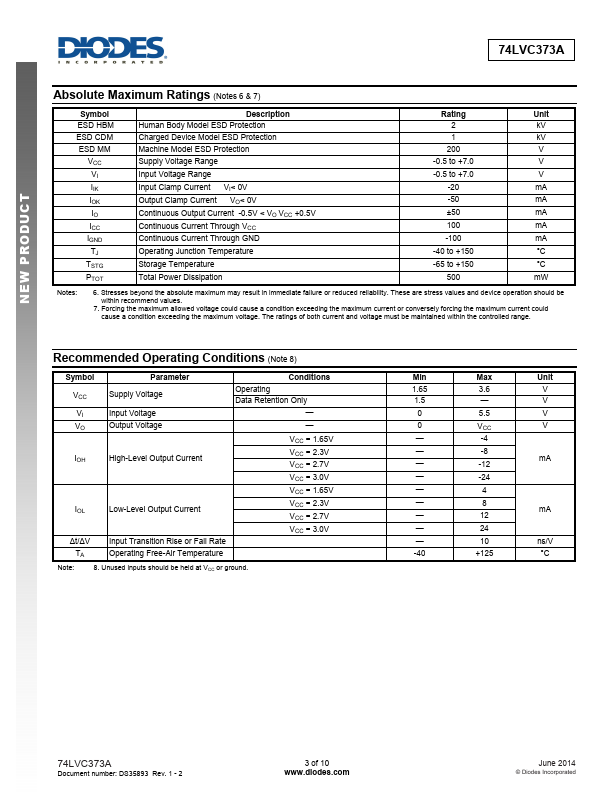

Datasheet Summary

NEW PRODUCT

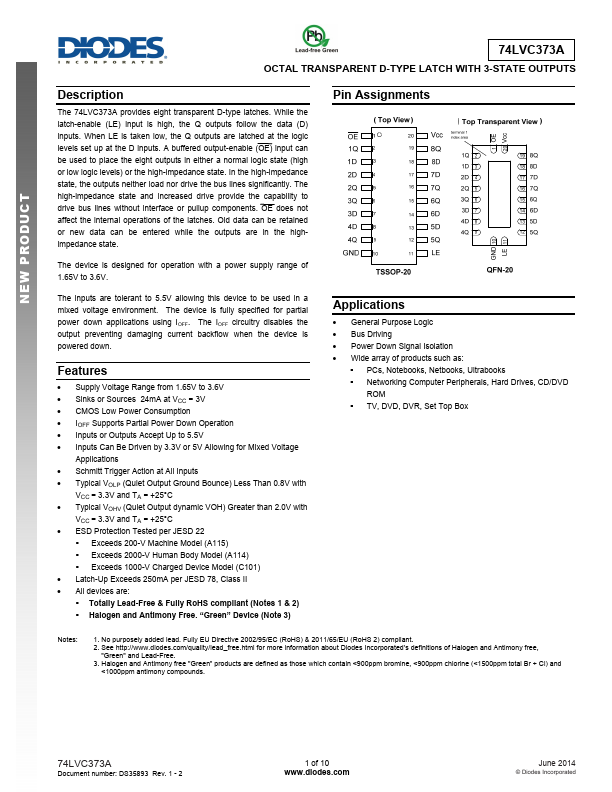

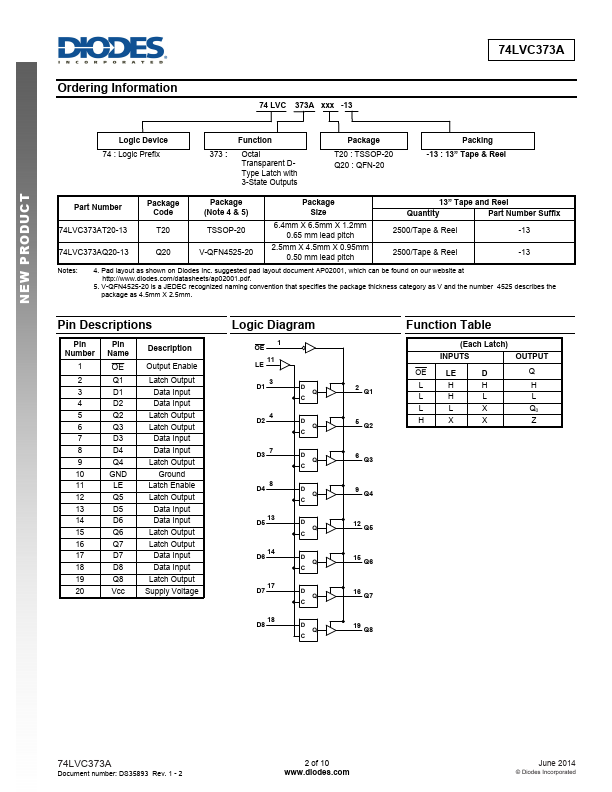

OCTAL TRANSPARENT D-TYPE LATCH WITH 3-STATE OUTPUTS

Description

The 74LVC373A provides eight transparent D-type latches. While the latch-enable (LE) input is high, the Q outputs follow the data (D) inputs. When LE is taken low, the Q outputs are latched at the logic levels set up at the D inputs. A buffered output-enable (OE) input can be used to place the eight outputs in either a normal logic state (high or low logic levels) or the high-impedance state. In the high-impedance state, the outputs neither load nor drive the bus lines significantly. The high-impedance state and increased drive provide the capability to drive bus lines without interface or pullup...