EDI8464P

EDI8464P is High Speed 256K Monolithic SRAM manufactured by EDI.

- Part of the EDI8464C comparator family.

- Part of the EDI8464C comparator family.

~EDI

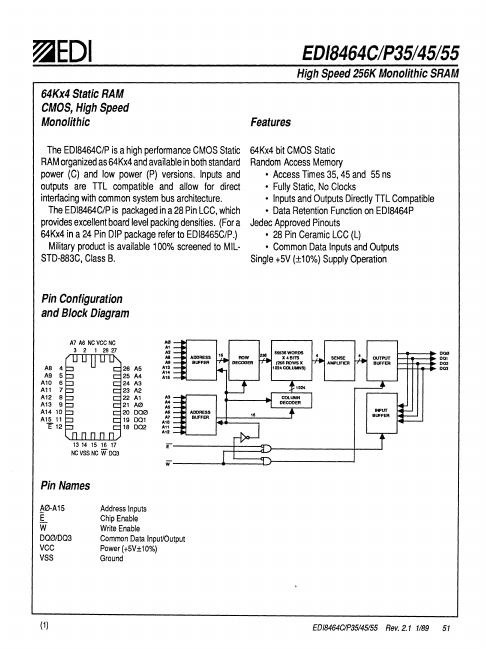

64Kx4 Static RAM CMOS, High Speed Monolithic

EDI8464CIP35145155

High Speed 256K Monolithic SRAM

Features

The EDI8464C/P is ahigh performance CMOS Static 64Kx4 bit CMOS Static

RAM organized as 64Kx4 and available in both standard Random Access Memory power (C) and low power (P) versions. Inputs and

- Access Times 35, 45 and 55 ns outputs are TTL patible and allow for direct

- Fully Static, No Clocks interfacing with mon system bus architecture.

- Inputs and Outputs Directly TTL patible

The EDI8464C/P is packaged in a28 Pin LCC, which

- Data Retention Function on EDI8464P provides excellent board level packing densities. (For a Jedec Approved Pinouts

64Kx4 in a 24 Pin DIP package refer to EDI8465C/P.)

- 28 Pin Ceramic LCC (L)

Military product is available 100% screened to MIL-

- mon Data Inputs and Outputs

STD-883C, Class B.

Single +5V (±10%) Supply Operation

Pin Configuration and Block Diagram

A8 4

A9 5 Al0 6 All 7 A12 8 A13 9 A1410 A1511

1: 12

N1C3v1s4s

15 NC

V16i

17 OQ3

All ........r

- -

-...