M12L64164A-7TG2C

M12L64164A-7TG2C is 1M x 16 Bit x 4 Banks Synchronous DRAM manufactured by Elite Semiconductor Microelectronics Technology.

- Part of the M12L64164A comparator family.

- Part of the M12L64164A comparator family.

ESMT

SDRAM

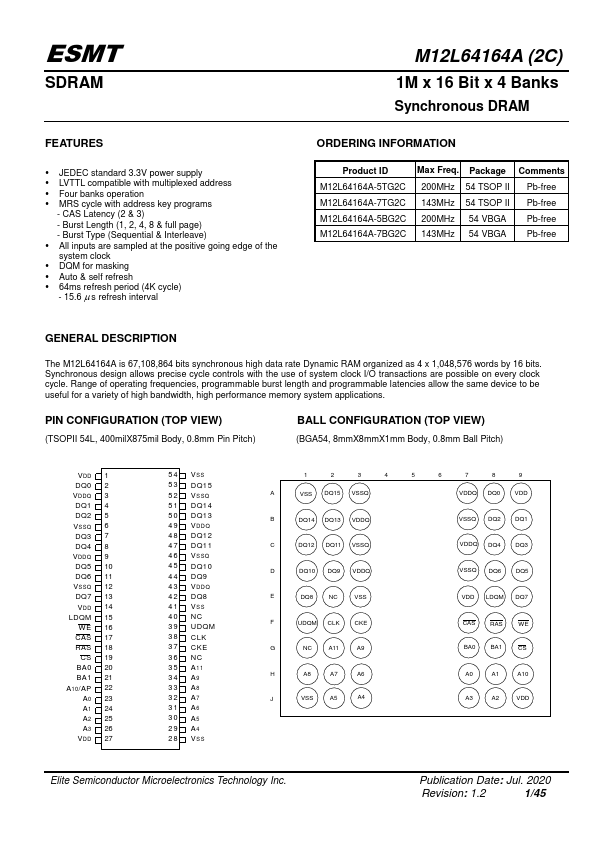

Features

- JEDEC standard 3.3V power supply

- LVTTL patible with multiplexed address

- Four banks operation

- MRS cycle with address key programs

- CAS Latency (2 & 3)

- Burst Length (1, 2, 4, 8 & full page)

- Burst Type (Sequential & Interleave)

- All inputs are sampled at the positive going edge of the system clock

- DQM for masking

- Auto & self refresh

- 64ms refresh period (4K cycle)

- 15.6 s refresh interval

M12L64164A (2C)

1M x 16 Bit x 4 Banks

Synchronous DRAM

ORDERING INFORMATION

Product ID

Max Freq. Package ments

M12L64164A-5TG2C 200MHz 54 TSOP II Pb-free

M12L64164A-7TG2C 143MHz 54 TSOP II Pb-free

M12L64164A-5BG2C 200MHz 54 VBGA Pb-free

M12L64164A-7BG2C...