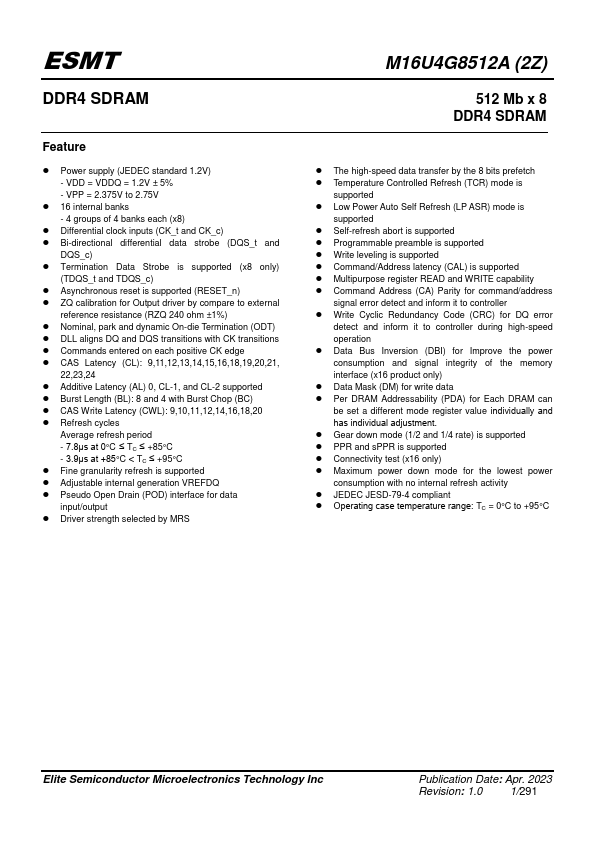

M16U4G8512A-QLBG2Z

M16U4G8512A-QLBG2Z is 512 Mb x 8 DDR4 SDRAM manufactured by Elite Semiconductor Microelectronics Technology.

Feature

- Power supply (JEDEC standard 1.2V)

- VDD = VDDQ = 1.2V ± 5%

- VPP = 2.375V to 2.75V

- 16 internal banks

- 4 groups of 4 banks each (x8)

- Differential clock inputs (CK_t and CK_c)

- Bi-directional differential data strobe (DQS_t and

DQS_c)

- Termination Data Strobe is supported (x8 only)

(TDQS_t and TDQS_c)

- Asynchronous reset is supported (RESET_n)

- ZQ calibration for Output driver by pare to external reference resistance (RZQ 240 ohm ±1%)

- Nominal, park and dynamic On-die Termination (ODT)

- DLL aligns DQ and DQS transitions with CK transitions

- mands entered on each positive CK edge

- CAS Latency (CL): 9,11,12,13,14,15,16,18,19,20,21,

22,23,24

- Additive Latency (AL) 0, CL-1, and CL-2 supported

- Burst Length (BL): 8 and 4 with Burst Chop (BC)

- CAS Write Latency (CWL): 9,10,11,12,14,16,18,20

- Refresh cycles

Average refresh period

- 7.8μs at 0°C ≤ TC ≤ +85°C

- 3.9μs at +85°C < TC ≤ +95°C

- Fine granularity refresh is supported

- Adjustable internal generation VREFDQ

- Pseudo Open Drain (POD) interface for data input/output

- Driver strength selected by MRS

M16U4G8512A (2Z)

512 Mb x 8 DDR4 SDRAM

- The high-speed data transfer by the 8 bits prefetch

- Temperature Controlled Refresh (TCR) mode is supported

- Low Power Auto Self Refresh (LP ASR) mode is supported

- Self-refresh abort is supported

- Programmable preamble is supported

- Write leveling is supported

- mand/Address latency (CAL) is supported

- Multipurpose register READ and WRITE capability

- mand Address (CA) Parity for mand/address signal error detect and inform it to...