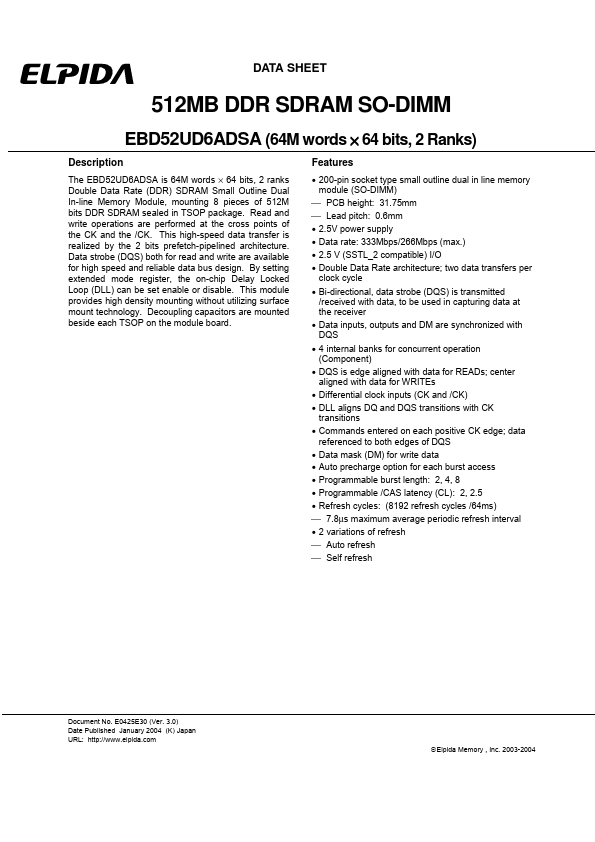

EBD52UD6ADSA

Overview

The EBD52UD6ADSA is 64M words × 64 bits, 2 ranks Double Data Rate (DDR) SDRAM Small Outline Dual In-line Memory Module, mounting 8 pieces of 512M bits DDR SDRAM sealed in TSOP package. Read and write operations are performed at the cross points of the CK and the /CK.

- 200-pin socket type small outline dual in line memory module (SO-DIMM) PCB height: 31.75mm Lead pitch: 0.6mm

- 2.5V power supply

- Data rate: 333Mbps/266Mbps (max.)

- 2.5 V (SSTL_2 compatible) I/O

- Double Data Rate architecture; two data transfers per clock cycle

- Bi-directional, data strobe (DQS) is transmitted /received with data, to be used in capturing data at the receiver

- Data inputs, outputs and DM are synchronized with DQS

- 4 internal banks for concurrent operation (Component)

- DQS is edge aligned with data for READs; center aligned with data for WRITEs

- Differential clock inputs (CK and /CK)