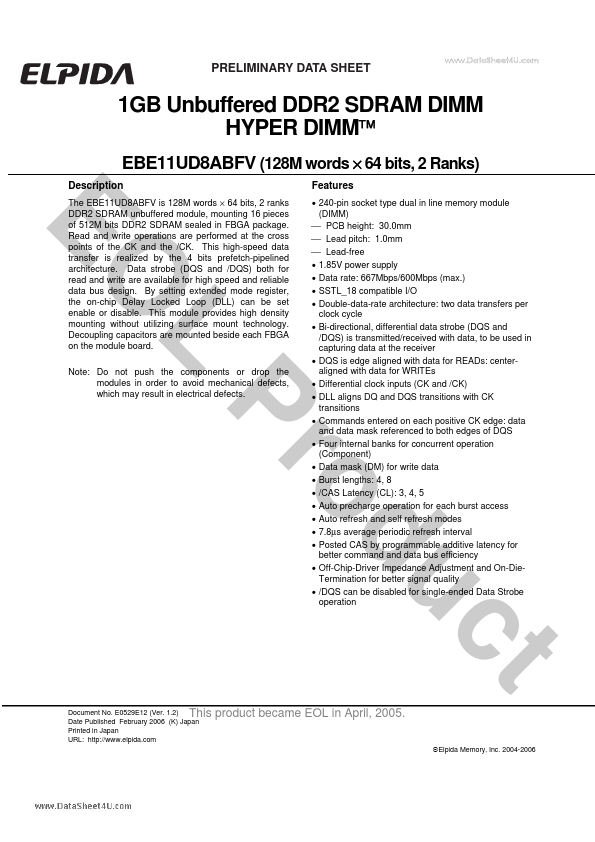

EBE11UD8ABFV

EBE11UD8ABFV is 1GB Unbuffered DDR2 SDRAM DIMM HYPER DIMM manufactured by Elpida Memory.

PRELIMINARY DATA SHEET

..

1GB Unbuffered DDR2 SDRAM DIMM HYPER DIMM

EBE11UD8ABFV (128M words × 64 bits, 2 Ranks)

Description

The EBE11UD8ABFV is 128M words × 64 bits, 2 ranks DDR2 SDRAM unbuffered module, mounting 16 pieces of 512M bits DDR2 SDRAM sealed in FBGA package. Read and write operations are performed at the cross points of the CK and the /CK. This high-speed data transfer is realized by the 4 bits prefetch-pipelined architecture. Data strobe (DQS and /DQS) both for read and write are available for high speed and reliable data bus design. By setting extended mode register, the on-chip Delay Locked Loop (DLL) can be set enable or disable. This module provides high density mounting without utilizing surface mount technology. Decoupling capacitors are mounted beside each FBGA on the module board. Note: Do not push the ponents or drop the modules in order to avoid mechanical defects, which may result in electrical defects.

Features

- 240-pin socket type dual in line memory module (DIMM) PCB height: 30.0mm Lead pitch: 1.0mm Lead-free

- 1.85V power supply

- Data rate: 667Mbps/600Mbps (max.)

- SSTL_18 patible I/O

- Double-data-rate architecture: two data transfers per clock cycle

- Bi-directional, differential data strobe (DQS and /DQS) is transmitted/received with data, to be used in capturing data at the receiver

- DQS is edge aligned with data for READs: centeraligned with data for WRITEs

- Differential clock inputs (CK and /CK)

- DLL aligns DQ and DQS transitions with CK transitions

- mands entered on each positive CK edge: data and data mask referenced to both edges of DQS

- Four internal banks for concurrent operation (ponent)

- Data mask (DM) for write data

- Burst lengths: 4, 8

- /CAS Latency (CL): 3, 4, 5

- Auto precharge operation for each burst access

- Auto refresh and self refresh modes

- 7.8µs average periodic refresh interval

- Posted CAS by programmable additive latency for better mand and data bus...