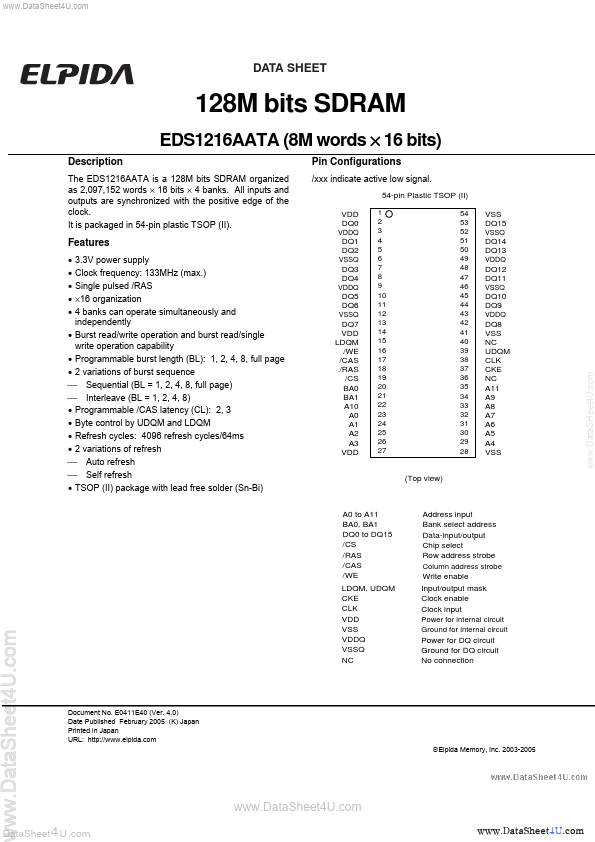

EDS1216AATA

Description

The EDS1216AATA is a 128M bits SDRAM organized as 2,097,152 words × 16 bits × 4 banks.

Key Features

- 3.3V power supply Clock frequency: 133MHz (max.) Single pulsed /RAS ×16 organization 4 banks can operate simultaneously and independently

- Burst read/write operation and burst read/single write operation capability

- Programmable burst length (BL): 1, 2, 4, 8, full page

- 2 variations of burst sequence Sequential (BL = 1, 2, 4, 8, full page) Interleave (BL = 1, 2, 4, 8)

- Programmable /CAS latency (CL): 2, 3

- Refresh cycles: 4096 refresh cycles/64ms

- 2 variations of refresh Auto refresh Self refresh