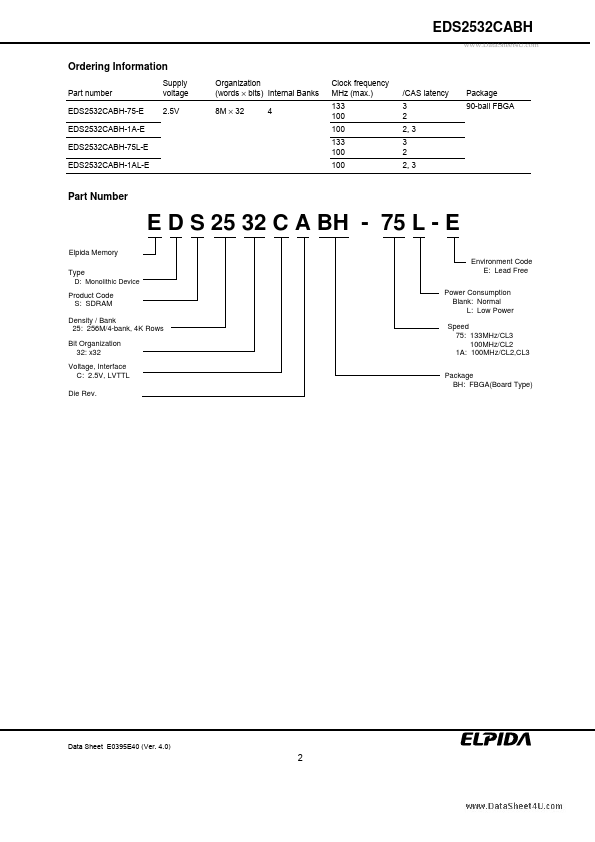

Datasheet Summary

..

DATA SHEET

256M bits SDRAM

EDS2532CABH (8M words × 32 bits)

Description

The EDS2532CABH is a 256M bits SDRAM organized as 2,097,152 words × 32 bits × 4 banks. All inputs and outputs are synchronized with the positive edge of the clock. It is packaged in 90-ball FBGA.

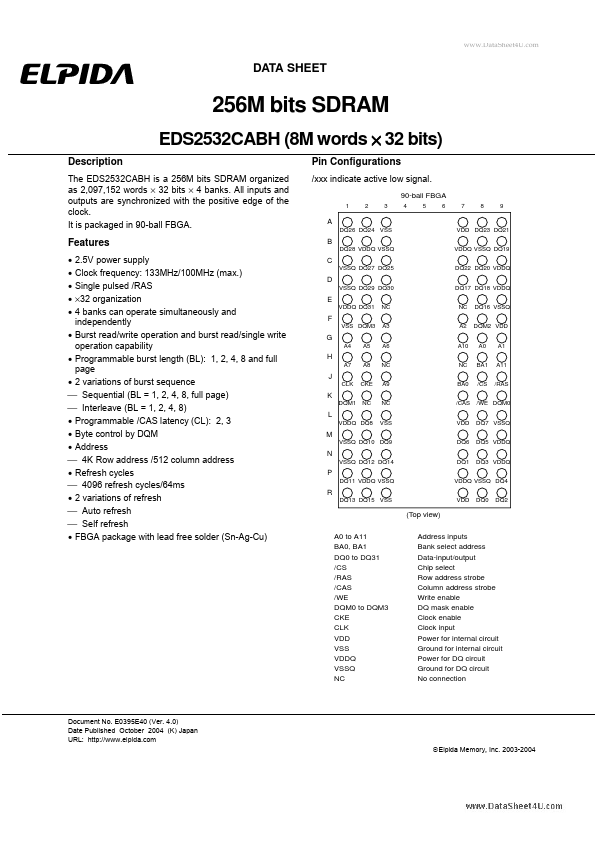

Pin Configurations

/xxx indicate active low signal.

90-ball FBGA

1 2 3 4 5 6 7 8 9

DQ26 DQ24 VSS VDD DQ23 DQ21 VDDQ VSSQ DQ19 DQ22 DQ20 VDDQ DQ17 DQ18 VDDQ NC A2 A10 NC BA0 /CAS VDD DQ6 DQ1 DQ16 VSSQ DQM2 VDD A0 BA1 /CS A1 A11 /RAS

Features

- -

- -

- 2.5V power supply Clock frequency: 133MHz/100MHz (max.) Single pulsed /RAS ×32 organization 4 banks can operate simultaneously and independently

- Burst...